MPC9352AC 電路輸出管的漏極和電源

發布時間:2020/2/9 12:57:52 訪問次數:8336

mpc9352accmos異或門電路如圖3.1.15所示。它由一級或非門和一級與或非門組成。或非門的輸出x=a+b。而與或非門的輸出l即為輸人a、b的異或e=a・b+9c=a・b+a+b=c;b+a・b=aob=hob;z=aob

圖3.1.15 異或門電路

如在異或門的后面增加一級反相器就構成異或非門,由于具有l=a・b+c・b的功能,因而稱為同或門。

輸入、輸出保護電路和緩沖電路,輸入保護緩沖電路,基本邏輯功能電路,輸出緩沖電路.

圖3.1.16 實際集成cmos門電路結構圖

cmos邏輯門通常接人輸入、輸出保護電路和緩沖電路,其電路結構圖如圖3.1.16所示,圖中的基本邏輯功能電路可以是前面介紹的反相器、與非門、或非閘或者它們的組合等任意一種電路。由于這些緩沖電路具有統一的參數,使得集成邏輯門電路的輸人和輸出特性,不再因內部邏輯不同而發生變化,從而使電路的性能得到改善。

輸入保護電路,cmos門電路的輸人端是mos管的柵極,在柵極與溝道之間是很薄的.

mos邏輯電路,基本邏輯,功能電路分別加以討論。

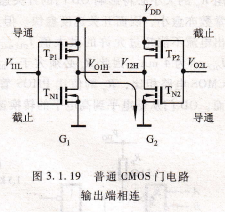

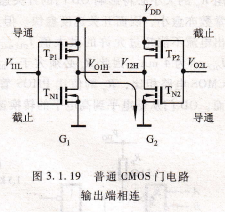

cmos漏極開路門電路,漏極開路門電路的結構及符號,在工程實踐中,往往需要將兩個門的輸出端并聯以實現與邏輯的功能稱為線與。現在來考察一種情況,如果將兩個cmos反相器g1和g2的輸出端連接在一起,如圖3.1.19所示,并設gi的ud,輸出處于高電平,tp1導通;而g2的輸出為低電平,tn2導通。這樣,從g1的tp1到g2的tn2將形成一低阻通路,從而巧1l=tplu2l,產生很大的電流,有可能導致器件的損毀,并且無法確定輸出是高電平還是低電平。這一問題可以采用漏極開路導通.

(0d①)門來解決。所謂漏極開路是cmos門輸出電路只有nmos管,并且普通cmos門電路,它的漏極是開路的。漏極開路的與非門輸出端相連,電路及符號如圖3.1.20(a)和3.1.20(b)所示,其中圖標“Ω”表示漏極開路之意。為了實現線與的邏輯功能,可將多個門電路輸出管的漏極和電源ydd之間,加一公共的上拉電阻rp②,如圖漏極開路輸出邏輯圖.

0d系0pen drain的縮寫。

上拉電阻系pul⒈up resistor的譯稱。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

mpc9352accmos異或門電路如圖3.1.15所示。它由一級或非門和一級與或非門組成。或非門的輸出x=a+b。而與或非門的輸出l即為輸人a、b的異或e=a・b+9c=a・b+a+b=c;b+a・b=aob=hob;z=aob

圖3.1.15 異或門電路

如在異或門的后面增加一級反相器就構成異或非門,由于具有l=a・b+c・b的功能,因而稱為同或門。

輸入、輸出保護電路和緩沖電路,輸入保護緩沖電路,基本邏輯功能電路,輸出緩沖電路.

圖3.1.16 實際集成cmos門電路結構圖

cmos邏輯門通常接人輸入、輸出保護電路和緩沖電路,其電路結構圖如圖3.1.16所示,圖中的基本邏輯功能電路可以是前面介紹的反相器、與非門、或非閘或者它們的組合等任意一種電路。由于這些緩沖電路具有統一的參數,使得集成邏輯門電路的輸人和輸出特性,不再因內部邏輯不同而發生變化,從而使電路的性能得到改善。

輸入保護電路,cmos門電路的輸人端是mos管的柵極,在柵極與溝道之間是很薄的.

mos邏輯電路,基本邏輯,功能電路分別加以討論。

cmos漏極開路門電路,漏極開路門電路的結構及符號,在工程實踐中,往往需要將兩個門的輸出端并聯以實現與邏輯的功能稱為線與。現在來考察一種情況,如果將兩個cmos反相器g1和g2的輸出端連接在一起,如圖3.1.19所示,并設gi的ud,輸出處于高電平,tp1導通;而g2的輸出為低電平,tn2導通。這樣,從g1的tp1到g2的tn2將形成一低阻通路,從而巧1l=tplu2l,產生很大的電流,有可能導致器件的損毀,并且無法確定輸出是高電平還是低電平。這一問題可以采用漏極開路導通.

(0d①)門來解決。所謂漏極開路是cmos門輸出電路只有nmos管,并且普通cmos門電路,它的漏極是開路的。漏極開路的與非門輸出端相連,電路及符號如圖3.1.20(a)和3.1.20(b)所示,其中圖標“Ω”表示漏極開路之意。為了實現線與的邏輯功能,可將多個門電路輸出管的漏極和電源ydd之間,加一公共的上拉電阻rp②,如圖漏極開路輸出邏輯圖.

0d系0pen drain的縮寫。

上拉電阻系pul⒈up resistor的譯稱。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

熱門點擊

熱門點擊

- LT1510IG 數值比較器的位數擴展

- IRF1405 真值表的內容填人四變量卡諾圖

- LM2936BM-5.0 功率變換組件的三部分

- XCR3384XL-10FG324I 變壓器鐵芯有卷環E型和卷環Y型

- TM200RZ-24(2H) 發電機負載勵磁特性發電機空載

- RL1004-2910-97-D1 JFET的變壓器反饋式IC振蕩電路

- MAX3832UCB-D 匯流條短路故障及逆序保護

- MPC9352AC 電路輸出管的漏極和電源

- UC2002 表征門電路開關速度的參數

- SST39VF3201-70 轉換式觸點式舌簧管繼電器

推薦電子資訊

推薦電子資訊

- 2013中國醫療電子展覽會

- v\:* {behavior:url(#def... [詳細]

公網安備44030402000607

公網安備44030402000607