CMOS結構

發布時間:2015/11/13 21:31:14 訪問次數:2049

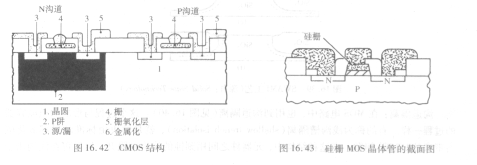

隔離問題,特別是對于CMOS結構來說,就是閂鎖效應(latch up)。圖16. 43是芯片部分的橫截面圖。NUD4001DR2G并排的MOS晶體管組成橫向的雙極型晶體管(NPN)。在電路工作過程中,雙極型晶體管扮演一個放大器的角色,但這不是我們希望看到的,它可以把輸出增大到使存儲器單元不能切換的狀態。這就是閂鎖效應。在這種狀況下,元器件對它的信息不能做出反應。避免閂鎖效應的一個辦法就是低電阻率的EPI外延層,這個外延層可以避開雙極型晶體

管的發射極從而使其不能“開”,從而達到防止閂鎖效應的目的。

局部氧化隔離涉及閂鎖效應。另一個解決辦法是用埋層來有效破壞橫向雙極型晶體管的加固良好的設計.

隔離問題,特別是對于CMOS結構來說,就是閂鎖效應(latch up)。圖16. 43是芯片部分的橫截面圖。NUD4001DR2G并排的MOS晶體管組成橫向的雙極型晶體管(NPN)。在電路工作過程中,雙極型晶體管扮演一個放大器的角色,但這不是我們希望看到的,它可以把輸出增大到使存儲器單元不能切換的狀態。這就是閂鎖效應。在這種狀況下,元器件對它的信息不能做出反應。避免閂鎖效應的一個辦法就是低電阻率的EPI外延層,這個外延層可以避開雙極型晶體

管的發射極從而使其不能“開”,從而達到防止閂鎖效應的目的。

局部氧化隔離涉及閂鎖效應。另一個解決辦法是用埋層來有效破壞橫向雙極型晶體管的加固良好的設計.

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607