地平面不完整產生EMI問題

發布時間:2017/6/7 20:57:29 訪問次數:946

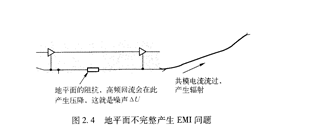

接地,盡管是EMC設計中最重要的方面,但是這個問題并不容易直觀理解,而且通常AAT2510IWP-AA-T1也很難建模或分析,囚為有許多無法控制的因素影響,導致很多工程師對此不理解。其實每個電路最終都要有一個參考接地源,這是無法選擇的事實,電路設計之初就應該首先考慮到 接地設計。接地是使不希望的噪聲、干擾極小化并對電路進行隔離劃分的一個重要方法。適當應用PCB的接地方法及電纜屏蔽將避免許多噪聲問題。設計良好的接地系統的一個優點就是以很低的成本防止不希望有的干擾及發射。還有,接地這個詞對不同領域的技術人員有不同的含義,本書中接地是一個比較廣泛的概念。對邏輯電路,它指邏輯電路和元件的參考電平,這個地也可以不連接到大地電位上,作為邏輯電壓參考地,其電位差的典型值必須小于毫伏級,如圖2.2所示的例子中,如果工作電平是3.3Ⅴ的T⒒電平,共模電流流過的接地平面引起的壓降大于0.4Ⅴ,就可能存在EMC測試通不過的危險;還有高速數字電路中的地平面不完整,如圖24所示,與地相連的電纜,由于被地平面上的噪聲驅動,就會產生EMI問題。對系統和結構,接地是指連接電路的金屬外盒或機架。對EMC測試,它是參考接地平面。

接地,盡管是EMC設計中最重要的方面,但是這個問題并不容易直觀理解,而且通常AAT2510IWP-AA-T1也很難建模或分析,囚為有許多無法控制的因素影響,導致很多工程師對此不理解。其實每個電路最終都要有一個參考接地源,這是無法選擇的事實,電路設計之初就應該首先考慮到 接地設計。接地是使不希望的噪聲、干擾極小化并對電路進行隔離劃分的一個重要方法。適當應用PCB的接地方法及電纜屏蔽將避免許多噪聲問題。設計良好的接地系統的一個優點就是以很低的成本防止不希望有的干擾及發射。還有,接地這個詞對不同領域的技術人員有不同的含義,本書中接地是一個比較廣泛的概念。對邏輯電路,它指邏輯電路和元件的參考電平,這個地也可以不連接到大地電位上,作為邏輯電壓參考地,其電位差的典型值必須小于毫伏級,如圖2.2所示的例子中,如果工作電平是3.3Ⅴ的T⒒電平,共模電流流過的接地平面引起的壓降大于0.4Ⅴ,就可能存在EMC測試通不過的危險;還有高速數字電路中的地平面不完整,如圖24所示,與地相連的電纜,由于被地平面上的噪聲驅動,就會產生EMI問題。對系統和結構,接地是指連接電路的金屬外盒或機架。對EMC測試,它是參考接地平面。

上一篇:產品的接地與EMC

公網安備44030402000607

公網安備44030402000607