差分對的詳細分析線電感和電容的分析

發布時間:2019/9/9 10:26:14 訪問次數:2914

線路電感和電容

案例1:奇數模式

案例2:偶數模式

單端阻抗

兩個串擾相關參數

差分對的詳細分析線電感和電容的分析

使用以下電路模型對無損單端傳輸線進行分析,得到無窮小的長度'delta x':

這里,'L'和'C'分別是線路每單位長度的電感和電容。經過分析,我們得出一條點的線的特征(或瞬時)阻抗由下式給出:

傳播延遲'Pd '給出了:.

我們現在可以將上述模型和結果應用于差分對線路的電感和電容分析參與其中。我們假設這樣的線條使得導體電阻('R'')和介電電導('G'')可以忽略阻抗和傳播延遲的目的。這將是感興趣的實際頻率的情況。

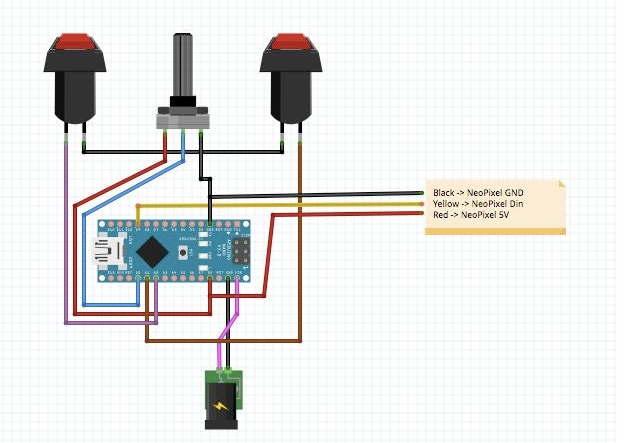

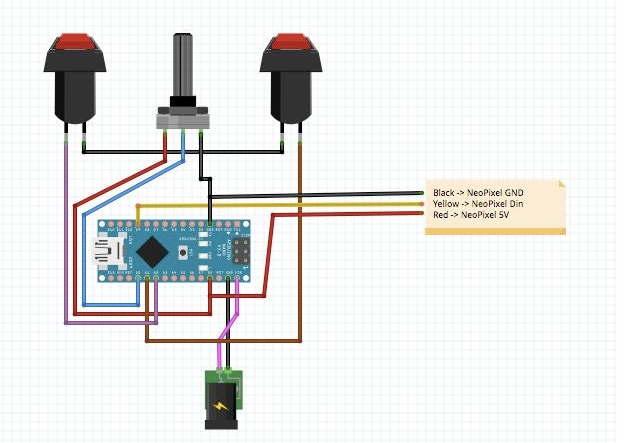

下圖給出了差分對線的無限小長度的電路模型:

這里'L0'和'C0'分別取決于每單位長度每條線的電感和電容。 'Lm'是第1行和第2行之間每單位長度的互感。'Cm'是第1行和第2行之間每單位長度的電容。

情況1:奇數模式(純差分信號)

這里'V2 = -V1'和'I2 = -I1'。因此,沒有電流在返回路徑中流動。 'Cm delta x'可以被認為是兩個電容器,每個電容器的值為“2Cm delta x”,其中心點為零電位。 (這是因為兩個相等電容之間的電位分壓。)因此,奇數模式下的等效電路變為:

讓我們來看看線路1(第2行情況完全相似)。

第1行的感應電壓由兩部分組成。一個歸因于'I',流過'L0 delta x'。另一個是由于'I2 = -I1',流過'Lm delta x'。這些可以等效地表示為由于'I',流過'(L0-Lm)delta x'。因此,奇數模式中線1的每單位長度的有效電感,由'Lodd'表示,將由下式給出:

有效電容在第1行和零電位線之間是'(C0 + 2Cm)delta x'。因此,每單位長度的奇模線電容是:

根據定義,類似于在單端線的情況下得到的結果,奇模特征阻抗由下式給出:

奇模信號的每單位長度傳播延遲由下式給出:

這是純單位信號差分部分的單位長度傳播延遲。此處還要記住的是,奇數模式或純差分信號的電磁波主要存在于兩條線之間的空間內和周圍。并且它們受參考或地平面的影響相對較小。

情況2:偶模式(純共模信號)

在這種情況下,'V2 = V1'并且由于該對中的兩行是相同的,'I1 = I2'。由于'V1 = V2',兩條線之間的電容'Cm'對兩條線中的電流沒有影響。因此可以忽略它,導致以下等效電路:

讓我們看一下第1行(第2行的情況相同)。

第1行的感應電壓將由'I1'貢獻,流入'L0 delta x'。并且通過'I2 = I1'',流入'Lm delta x'。這相當于說'I1'流過'(L0 + Lm)delta x'。因此,偶數模式下任一行的每單位長度的有效電感將為:

均勻模式下任一行的每單位長度有效電容將是:

因此,任一行的偶模阻抗將由下式給出:

偶模信號的每單位長度的傳播延遲由下式給出:

等式(13c)和(14c)清楚地表明' Zeven'比'Zodd'更重要。從理論上講,還知道'Lm'小于'L0','Cm'小于'C0'。

'Zse ','Zm'和'K'用'L0','C0','Lm','Cm'

使用等式(12),(13)和(14) ),我們有:

關于'Zse'的一些詞

'Zse'是存在兩條線的任一條中的單端阻抗另一條線。當沒有第二條線時,它與單條線的單端阻抗不完全相同。第二條線的存在稍微降低了阻抗。兩條線越耦合(或越接近),'Zse'將變得更少。

重要的是要注意,如果兩條線之間的耦合是'Zse',則變化不大。不高。或者,如果我們可以使兩條線之間的間隔大于信號層和最近的地面/參考平面之間的導體寬度或介電高度的最大值。

。如果間隔大于信號層和最近參考平面之間的介電高度,則“Zse”相對相同。

此外,'Zse'不接近'L0/C0'但更接近'L0/(C0 + Cm)'。乍一看似乎令人驚訝,但情況確實如此。

定義一些新術語并不合適:

'KL'和'KC'可以分別稱為電感和電容耦合系數。使用這些,我們可以將等式(15)寫成:

自'KL'和'KC'小于1,并且對于大多數實際案例將明顯小于1,我們只能保留一階項,以便:

如果我們將方程(18a)與(8a)和(18b)與(10a)進行比較,很容易得出結論:

并且:

值得一提的是,在大多數帶狀線差分對的實際情況中,歸納如果信號層上方和下方的PCB材料的介電常數幾乎相等,則耦合系數'KL'和電容耦合系數'KC'幾乎相等。

兩個串擾相關參數

在這里,我們還要定義另外兩個參數,NEXT和FEXT:

NEXT被稱為最近的串擾系數。 FEXT稱為遠端串擾系數。這些參數在串擾分析中是重要的,當兩條附近的線路中,一條是主信號線而另一條線是安靜的線路,我們希望在該線路上確定由于主線路上的信號電壓而引起的串擾電壓。我們將在下一篇關于串擾分析的文章中詳細闡述這一點。

差分線對中的兩個PCB線完全一致

高速設計規則通常也都適用于差分信號的布線

PCB設計布線非常靠近的差分信號對相互之間也會互相緊密耦合,這種互相之間的耦合會減小EMI發射,差分信號線的主要缺點是增加了PCB的面積,本文介紹電路板設計過程中采用差分信號線PCB設計布線的PCB設計布線策略。

眾所周知,信號存在沿信號線或者PCB線下面傳輸的特性,即便我們可能并不熟悉單端模式PCB設計布線策略,單端這個術語將信號的這種傳輸特性與差模和共模種信號傳輸方式區別開來,后面這兩種信號傳輸方式通常更為復雜。

差分和共模方式

差模信號通過一對信號線來傳輸。一個信號線上傳輸我們通常所理解的信號;另一個信號線上則傳輸一個等值而方向相反(至少在理論上是這樣)的信號。差分和單端模式最初出現時差異不大,因為所有的信號都存在回路。

單端模式的信號通常經由一個零電壓的電路(或者稱為地)來返回。差分信號中的每一個信號都要通過地電路來返回。由于每一個信號對實際上是等值而反向的,所以返回電路就簡單地互相抵消了,因此在零電壓或者是地電路上就不會出現差分信號返回的成分。

共模方式是指信號出現在一個(差分)信號線對的兩個信號線上,或者是同時出現在單端信號線和地上。對這個概念的理解并不直觀,因為很難想象如何產生這樣的信號。這主要是因為通常我們并不生成共模信號的緣故。共模信號絕大多數都是根據假想情況在電路中產生或者由鄰近的或外界的信號源耦合進來的噪聲信號。共模信號幾乎總是“有害的”,許多設計規則就是專為預防共模信號出現而設計的。

差分信號線的PCB設計布線

通常(當然也有一些例外)差分信號也是高速信號,所以高速設計規則通常也都適用于差分信號的PCB設計布線,特別是設計傳輸線這樣的信號線時更是如此。這就意味著我們必須非常謹慎地設計信號線的PCB設計布線,以確保信號線的特征阻抗沿信號線各處連續并且保持一個常數。

在差分線對的布局PCB設計布線過程中,我們希望差分線對中的兩個PCB線完全一致。這就意味著,在實際應用中應該盡最大的努力來確保差分線對中的PCB線具有完全一樣的阻抗并且PCB設計布線的長度也完全一致。差分PCB線通常總是成對PCB設計布線,而且它們之間的距離沿線對的方向在任意位置都保持為一個常數不變。通常情況下,差分線對的布局PCB設計布線總是盡可能地靠近。

差分信號的優勢

單端信號通常總是參照某種“參考”電平。這種“參考”電平可能是一個正值電壓也可能是地電壓、一個器件的閾值電壓、或者是其它什么地方的另外一個信號。而另一方面差分信號則總是參照該差分線對中的另一方。也就是說,如果一個信號線(+信號)上的電壓高于另一個信號線(-信號)上的電壓,那么我們就可以得到一種邏輯狀態;而如果前者低于后者那么我們就可以得到另外的一種邏輯狀態。

差分信號對EMI和信號之間的串擾耦合也具有一定的免疫能力。如果一對差分信號線對的PCB設計布線非常緊湊,那么任何外部耦合的噪聲都會相同程度地耦合到線對中的每一條信號線上。所以耦合的噪聲就成為“共模”噪聲,而差分信號電路對這種信號具有非常完美的免疫能力。如果線對是絞合在一起的(比如雙絞線),那么信號線對耦合噪聲的免疫能力會更強。由于不可能在PCB上很方便地實現差分信號的絞合,那么盡可能地將它們的PCB設計布線靠近在一起就成為實際應用中一種非常好的辦法。

PCB設計布線非常靠近的差分信號對相互之間也會互相緊密耦合。這種互相之間的耦合會減小EMI發射,特別是同單端PCB信號線相比。可以這樣想象,差分信號中每一條信號線對外的輻射是大小相等而方向相反,因此會相互抵消,就像信號在雙絞線中的情況一樣。差分信號在PCB設計布線時靠得越近,相互之間的耦合也就越強,因而對外的EMI輻射也就越小。

差分電路的主要缺點就是增加了PCB線。所以,如果應用過程中不能發揮差分信號的優點的話,那么不值得增加PCB面積。但是如果設計出的電路性能方面有重大改進的話,那么增加的PCB設計布線面積所付出的代價就是值得的。

差分信號線之間互相會耦合。這種耦合會影響信號線的外在阻抗,因此必須采用終端匹配策略(參見注解2中有關討論以及差分阻抗的計算)。差分阻抗的計算很困難,國家半導體在這個領域提供了一些參考。PolarInstruments也提供一個獨立的可以計算許多種不同的差分信號結構3的差分阻抗計算器(需要一些費用)。高端的設計工具包也可以計算差分阻抗。

差分信號具有如下幾個優點:1.時序得到精確的定義,這是由于控制信號線對的交叉點要比控制信號相對于一個參考電平的絕對電壓值來得簡單。這也是需要精確實現差分線對等長PCB設計布線的一個理由。如果信號不能同時到達差分線對的另一端的話,那么源端所能夠提供的任何時序的控制都會大打折扣。此外,如果差分線對遠端的信號并非嚴格意義上的等值而反向,那么就會出現共模噪聲,而這將導致信號時序和EMI方面的問題。2.由于差分信號并不參照它們自身以外的任何信號,并且可以更加嚴格地控制信號交叉點的時序,所以差分電路同常規的單端信號電路相比通常可以工作在更高的速度。

由于差分電路的工作取決于兩個信號線(它們的信號等值而反向)上信號之間的差值,同周圍的噪聲相比,得到的信號就是任何一個單端信號的兩倍大小。所以,在其它所有情況都一樣的條件下,差分信號總是具有更高的信噪比因而提供更高的性能。

差分電路對于差分對上的信號電平之間的差異非常靈敏。但是相對于一些其它的參考(尤其是地)來說,它們對于差分線上的絕對電壓值卻不敏感。相對來說,差分電路對于類似地彈反射和其它可能存在于電源和地平面上的噪聲信號等這樣的問題是不敏感的,而對共模信號來說,它們則會完全一致地出現在每一條信號線上。

但是要注意差分線之間的相互耦合將直接影響差分阻抗的計算。差分線之間的耦合必須保證沿整個差分線都保持為一個常數或者確保阻抗的連續性。這也是差分線之間必須保持“恒定間距”設計規則的原因。

免責聲明:

凡標注“來源:互聯網轉載”的文章均來自其他媒體,轉載的目的在于傳遞更多信息,并不代表本站觀點,圖片來源于網絡收集整理,版權歸原作者所有;如果發現本站有涉嫌抄襲,侵權內容,請發送郵件:602684288@qq舉報,并提供相關證據,一經查實,立刻刪除涉嫌侵權內容。

線路電感和電容

案例1:奇數模式

案例2:偶數模式

單端阻抗

兩個串擾相關參數

差分對的詳細分析線電感和電容的分析

使用以下電路模型對無損單端傳輸線進行分析,得到無窮小的長度'delta x':

這里,'L'和'C'分別是線路每單位長度的電感和電容。經過分析,我們得出一條點的線的特征(或瞬時)阻抗由下式給出:

傳播延遲'Pd '給出了:.

我們現在可以將上述模型和結果應用于差分對線路的電感和電容分析參與其中。我們假設這樣的線條使得導體電阻('R'')和介電電導('G'')可以忽略阻抗和傳播延遲的目的。這將是感興趣的實際頻率的情況。

下圖給出了差分對線的無限小長度的電路模型:

這里'L0'和'C0'分別取決于每單位長度每條線的電感和電容。 'Lm'是第1行和第2行之間每單位長度的互感。'Cm'是第1行和第2行之間每單位長度的電容。

情況1:奇數模式(純差分信號)

這里'V2 = -V1'和'I2 = -I1'。因此,沒有電流在返回路徑中流動。 'Cm delta x'可以被認為是兩個電容器,每個電容器的值為“2Cm delta x”,其中心點為零電位。 (這是因為兩個相等電容之間的電位分壓。)因此,奇數模式下的等效電路變為:

讓我們來看看線路1(第2行情況完全相似)。

第1行的感應電壓由兩部分組成。一個歸因于'I',流過'L0 delta x'。另一個是由于'I2 = -I1',流過'Lm delta x'。這些可以等效地表示為由于'I',流過'(L0-Lm)delta x'。因此,奇數模式中線1的每單位長度的有效電感,由'Lodd'表示,將由下式給出:

有效電容在第1行和零電位線之間是'(C0 + 2Cm)delta x'。因此,每單位長度的奇模線電容是:

根據定義,類似于在單端線的情況下得到的結果,奇模特征阻抗由下式給出:

奇模信號的每單位長度傳播延遲由下式給出:

這是純單位信號差分部分的單位長度傳播延遲。此處還要記住的是,奇數模式或純差分信號的電磁波主要存在于兩條線之間的空間內和周圍。并且它們受參考或地平面的影響相對較小。

情況2:偶模式(純共模信號)

在這種情況下,'V2 = V1'并且由于該對中的兩行是相同的,'I1 = I2'。由于'V1 = V2',兩條線之間的電容'Cm'對兩條線中的電流沒有影響。因此可以忽略它,導致以下等效電路:

讓我們看一下第1行(第2行的情況相同)。

第1行的感應電壓將由'I1'貢獻,流入'L0 delta x'。并且通過'I2 = I1'',流入'Lm delta x'。這相當于說'I1'流過'(L0 + Lm)delta x'。因此,偶數模式下任一行的每單位長度的有效電感將為:

均勻模式下任一行的每單位長度有效電容將是:

因此,任一行的偶模阻抗將由下式給出:

偶模信號的每單位長度的傳播延遲由下式給出:

等式(13c)和(14c)清楚地表明' Zeven'比'Zodd'更重要。從理論上講,還知道'Lm'小于'L0','Cm'小于'C0'。

'Zse ','Zm'和'K'用'L0','C0','Lm','Cm'

使用等式(12),(13)和(14) ),我們有:

關于'Zse'的一些詞

'Zse'是存在兩條線的任一條中的單端阻抗另一條線。當沒有第二條線時,它與單條線的單端阻抗不完全相同。第二條線的存在稍微降低了阻抗。兩條線越耦合(或越接近),'Zse'將變得更少。

重要的是要注意,如果兩條線之間的耦合是'Zse',則變化不大。不高。或者,如果我們可以使兩條線之間的間隔大于信號層和最近的地面/參考平面之間的導體寬度或介電高度的最大值。

。如果間隔大于信號層和最近參考平面之間的介電高度,則“Zse”相對相同。

此外,'Zse'不接近'L0/C0'但更接近'L0/(C0 + Cm)'。乍一看似乎令人驚訝,但情況確實如此。

定義一些新術語并不合適:

'KL'和'KC'可以分別稱為電感和電容耦合系數。使用這些,我們可以將等式(15)寫成:

自'KL'和'KC'小于1,并且對于大多數實際案例將明顯小于1,我們只能保留一階項,以便:

如果我們將方程(18a)與(8a)和(18b)與(10a)進行比較,很容易得出結論:

并且:

值得一提的是,在大多數帶狀線差分對的實際情況中,歸納如果信號層上方和下方的PCB材料的介電常數幾乎相等,則耦合系數'KL'和電容耦合系數'KC'幾乎相等。

兩個串擾相關參數

在這里,我們還要定義另外兩個參數,NEXT和FEXT:

NEXT被稱為最近的串擾系數。 FEXT稱為遠端串擾系數。這些參數在串擾分析中是重要的,當兩條附近的線路中,一條是主信號線而另一條線是安靜的線路,我們希望在該線路上確定由于主線路上的信號電壓而引起的串擾電壓。我們將在下一篇關于串擾分析的文章中詳細闡述這一點。

差分線對中的兩個PCB線完全一致

高速設計規則通常也都適用于差分信號的布線

PCB設計布線非常靠近的差分信號對相互之間也會互相緊密耦合,這種互相之間的耦合會減小EMI發射,差分信號線的主要缺點是增加了PCB的面積,本文介紹電路板設計過程中采用差分信號線PCB設計布線的PCB設計布線策略。

眾所周知,信號存在沿信號線或者PCB線下面傳輸的特性,即便我們可能并不熟悉單端模式PCB設計布線策略,單端這個術語將信號的這種傳輸特性與差模和共模種信號傳輸方式區別開來,后面這兩種信號傳輸方式通常更為復雜。

差分和共模方式

差模信號通過一對信號線來傳輸。一個信號線上傳輸我們通常所理解的信號;另一個信號線上則傳輸一個等值而方向相反(至少在理論上是這樣)的信號。差分和單端模式最初出現時差異不大,因為所有的信號都存在回路。

單端模式的信號通常經由一個零電壓的電路(或者稱為地)來返回。差分信號中的每一個信號都要通過地電路來返回。由于每一個信號對實際上是等值而反向的,所以返回電路就簡單地互相抵消了,因此在零電壓或者是地電路上就不會出現差分信號返回的成分。

共模方式是指信號出現在一個(差分)信號線對的兩個信號線上,或者是同時出現在單端信號線和地上。對這個概念的理解并不直觀,因為很難想象如何產生這樣的信號。這主要是因為通常我們并不生成共模信號的緣故。共模信號絕大多數都是根據假想情況在電路中產生或者由鄰近的或外界的信號源耦合進來的噪聲信號。共模信號幾乎總是“有害的”,許多設計規則就是專為預防共模信號出現而設計的。

差分信號線的PCB設計布線

通常(當然也有一些例外)差分信號也是高速信號,所以高速設計規則通常也都適用于差分信號的PCB設計布線,特別是設計傳輸線這樣的信號線時更是如此。這就意味著我們必須非常謹慎地設計信號線的PCB設計布線,以確保信號線的特征阻抗沿信號線各處連續并且保持一個常數。

在差分線對的布局PCB設計布線過程中,我們希望差分線對中的兩個PCB線完全一致。這就意味著,在實際應用中應該盡最大的努力來確保差分線對中的PCB線具有完全一樣的阻抗并且PCB設計布線的長度也完全一致。差分PCB線通常總是成對PCB設計布線,而且它們之間的距離沿線對的方向在任意位置都保持為一個常數不變。通常情況下,差分線對的布局PCB設計布線總是盡可能地靠近。

差分信號的優勢

單端信號通常總是參照某種“參考”電平。這種“參考”電平可能是一個正值電壓也可能是地電壓、一個器件的閾值電壓、或者是其它什么地方的另外一個信號。而另一方面差分信號則總是參照該差分線對中的另一方。也就是說,如果一個信號線(+信號)上的電壓高于另一個信號線(-信號)上的電壓,那么我們就可以得到一種邏輯狀態;而如果前者低于后者那么我們就可以得到另外的一種邏輯狀態。

差分信號對EMI和信號之間的串擾耦合也具有一定的免疫能力。如果一對差分信號線對的PCB設計布線非常緊湊,那么任何外部耦合的噪聲都會相同程度地耦合到線對中的每一條信號線上。所以耦合的噪聲就成為“共模”噪聲,而差分信號電路對這種信號具有非常完美的免疫能力。如果線對是絞合在一起的(比如雙絞線),那么信號線對耦合噪聲的免疫能力會更強。由于不可能在PCB上很方便地實現差分信號的絞合,那么盡可能地將它們的PCB設計布線靠近在一起就成為實際應用中一種非常好的辦法。

PCB設計布線非常靠近的差分信號對相互之間也會互相緊密耦合。這種互相之間的耦合會減小EMI發射,特別是同單端PCB信號線相比。可以這樣想象,差分信號中每一條信號線對外的輻射是大小相等而方向相反,因此會相互抵消,就像信號在雙絞線中的情況一樣。差分信號在PCB設計布線時靠得越近,相互之間的耦合也就越強,因而對外的EMI輻射也就越小。

差分電路的主要缺點就是增加了PCB線。所以,如果應用過程中不能發揮差分信號的優點的話,那么不值得增加PCB面積。但是如果設計出的電路性能方面有重大改進的話,那么增加的PCB設計布線面積所付出的代價就是值得的。

差分信號線之間互相會耦合。這種耦合會影響信號線的外在阻抗,因此必須采用終端匹配策略(參見注解2中有關討論以及差分阻抗的計算)。差分阻抗的計算很困難,國家半導體在這個領域提供了一些參考。PolarInstruments也提供一個獨立的可以計算許多種不同的差分信號結構3的差分阻抗計算器(需要一些費用)。高端的設計工具包也可以計算差分阻抗。

差分信號具有如下幾個優點:1.時序得到精確的定義,這是由于控制信號線對的交叉點要比控制信號相對于一個參考電平的絕對電壓值來得簡單。這也是需要精確實現差分線對等長PCB設計布線的一個理由。如果信號不能同時到達差分線對的另一端的話,那么源端所能夠提供的任何時序的控制都會大打折扣。此外,如果差分線對遠端的信號并非嚴格意義上的等值而反向,那么就會出現共模噪聲,而這將導致信號時序和EMI方面的問題。2.由于差分信號并不參照它們自身以外的任何信號,并且可以更加嚴格地控制信號交叉點的時序,所以差分電路同常規的單端信號電路相比通常可以工作在更高的速度。

由于差分電路的工作取決于兩個信號線(它們的信號等值而反向)上信號之間的差值,同周圍的噪聲相比,得到的信號就是任何一個單端信號的兩倍大小。所以,在其它所有情況都一樣的條件下,差分信號總是具有更高的信噪比因而提供更高的性能。

差分電路對于差分對上的信號電平之間的差異非常靈敏。但是相對于一些其它的參考(尤其是地)來說,它們對于差分線上的絕對電壓值卻不敏感。相對來說,差分電路對于類似地彈反射和其它可能存在于電源和地平面上的噪聲信號等這樣的問題是不敏感的,而對共模信號來說,它們則會完全一致地出現在每一條信號線上。

但是要注意差分線之間的相互耦合將直接影響差分阻抗的計算。差分線之間的耦合必須保證沿整個差分線都保持為一個常數或者確保阻抗的連續性。這也是差分線之間必須保持“恒定間距”設計規則的原因。

免責聲明:

凡標注“來源:互聯網轉載”的文章均來自其他媒體,轉載的目的在于傳遞更多信息,并不代表本站觀點,圖片來源于網絡收集整理,版權歸原作者所有;如果發現本站有涉嫌抄襲,侵權內容,請發送郵件:602684288@qq舉報,并提供相關證據,一經查實,立刻刪除涉嫌侵權內容。

熱門點擊

熱門點擊

- 顯示技術中的顯示器件種類繁多,

- 數據采集系統是智能儀器的重要組成部分

- IC 7400工作及其應用

- 華為手機芯片一部分是自己生產的稱為“華為麒麟

- 零序電容電流補償法

- 各種電子電路都需要直流電源供電

- 差分對的詳細分析線電感和電容的分析

- 邏輯分析儀的分類

- 2020年,中國芯片產業與國際先進水平之間的

- OPT3007超薄環境光傳感器

推薦技術資料

推薦技術資料

- 單片機版光立方的制作

- N視頻: http://v.youku.comN_sh... [詳細]

公網安備44030402000607

公網安備44030402000607