MAX902EPD 時序電路的邏輯功能

發布時間:2019/10/8 12:15:18 訪問次數:2108

MAX902EPD圖1.1.4 數字波形

(a)非周期性數字波形 (b)周期性數字波形

周期性數字波形常用周期r和頻率r來描述。脈沖波形的脈沖寬度用fw表示,它表示脈沖的作用時間。另一個重要參數是占空比g,它表示脈沖寬度Tw占整個周期T的百分數,常用下式來表示

當占空比為50%時,稱此時的矩形脈沖為方波,即0和1交替出現并持續占有相同的時間。

例1,1,2 設周期性數字波形的高電平持續6 ms,低電平持續10 ms,求占空比g。

解:因數字波形的脈沖寬度Jw=6 ms,周期r=(6+1o)ms=16 ms

g=甘%・三號飛×100% 375%

實際數字信號波形

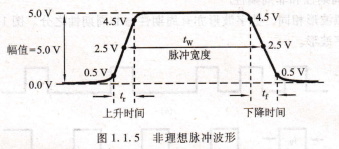

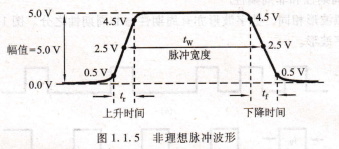

在實際的數字系統中,數字信號并沒有那么理想。當它從低電平跳變到高電平,或從高電平跳到低電平時,邊沿沒有那么陡峭,而要經歷一個過渡過程,分別用上升時間rr和下降時間莎r描述,如圖1.1.5所示。將脈沖幅值的10%到90%時所經歷的時間稱為上升時間rr。下降時間則相反,從脈沖幅值的90%下降到10%時所經歷的時間稱為下降時間莎f。將脈沖幅值的50%的兩個時間點所跨越的時間稱為脈沖寬度Jw,對于不同類型的器件和電路,其上升和下降時間各不相同。一般數字信號上升和下降時間的典型值約為幾納秒(ns)。

圖1,1.5 非理想脈沖波形

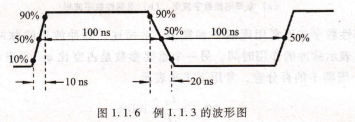

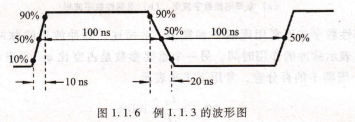

例1.1^3 試繪出一脈沖波形,設它的占空比為50%,脈沖寬度為100 ns,上升時間為10 ns,而下降時間為20 ns。

解:根據題意,所繪出的脈沖波形如圖1.1.6所示。

圖1.1.6 例1.1.3的波形圖

本書所用的數字波形大多數將畫成理想波形。實際上,每一波形均有上升時間和下降時間。由于rr和Jf與脈沖寬度的時間相比非常小,則不必在每一波形上表示出來。畫波形的目的只是為了知道高、低電平所經歷的時間。

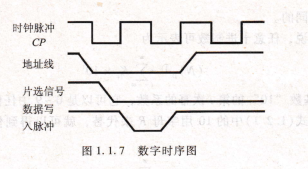

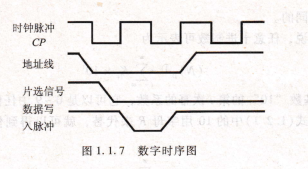

時序圖,在數字電路中,常用時序圖或稱為脈沖波形圖,來分析時序電路的邏輯功能。表明各信號之間時序關系的波形圖稱為時序圖。圖1,1.7所示為一典型的時序圖。圖中CP為時鐘脈沖信號,它是數字系統中的時間參考信號。地址線、片選和數據寫入等信號亦示于圖1.1.7中。關于時序圖中各個波形的具體作用,將在后續章節中介紹。通常數字集成電路,例如存儲器和時序邏輯器件等均須附有時序圖,以便于進行數字系統的分析、設計和應用。

MAX902EPD圖1.1.4 數字波形

(a)非周期性數字波形 (b)周期性數字波形

周期性數字波形常用周期r和頻率r來描述。脈沖波形的脈沖寬度用fw表示,它表示脈沖的作用時間。另一個重要參數是占空比g,它表示脈沖寬度Tw占整個周期T的百分數,常用下式來表示

當占空比為50%時,稱此時的矩形脈沖為方波,即0和1交替出現并持續占有相同的時間。

例1,1,2 設周期性數字波形的高電平持續6 ms,低電平持續10 ms,求占空比g。

解:因數字波形的脈沖寬度Jw=6 ms,周期r=(6+1o)ms=16 ms

g=甘%・三號飛×100% 375%

實際數字信號波形

在實際的數字系統中,數字信號并沒有那么理想。當它從低電平跳變到高電平,或從高電平跳到低電平時,邊沿沒有那么陡峭,而要經歷一個過渡過程,分別用上升時間rr和下降時間莎r描述,如圖1.1.5所示。將脈沖幅值的10%到90%時所經歷的時間稱為上升時間rr。下降時間則相反,從脈沖幅值的90%下降到10%時所經歷的時間稱為下降時間莎f。將脈沖幅值的50%的兩個時間點所跨越的時間稱為脈沖寬度Jw,對于不同類型的器件和電路,其上升和下降時間各不相同。一般數字信號上升和下降時間的典型值約為幾納秒(ns)。

圖1,1.5 非理想脈沖波形

例1.1^3 試繪出一脈沖波形,設它的占空比為50%,脈沖寬度為100 ns,上升時間為10 ns,而下降時間為20 ns。

解:根據題意,所繪出的脈沖波形如圖1.1.6所示。

圖1.1.6 例1.1.3的波形圖

本書所用的數字波形大多數將畫成理想波形。實際上,每一波形均有上升時間和下降時間。由于rr和Jf與脈沖寬度的時間相比非常小,則不必在每一波形上表示出來。畫波形的目的只是為了知道高、低電平所經歷的時間。

時序圖,在數字電路中,常用時序圖或稱為脈沖波形圖,來分析時序電路的邏輯功能。表明各信號之間時序關系的波形圖稱為時序圖。圖1,1.7所示為一典型的時序圖。圖中CP為時鐘脈沖信號,它是數字系統中的時間參考信號。地址線、片選和數據寫入等信號亦示于圖1.1.7中。關于時序圖中各個波形的具體作用,將在后續章節中介紹。通常數字集成電路,例如存儲器和時序邏輯器件等均須附有時序圖,以便于進行數字系統的分析、設計和應用。

公網安備44030402000607

公網安備44030402000607