ZRU3V6B-HF 實數型常量進行存儲和運算

發布時間:2019/10/10 13:17:19 訪問次數:1075

ZRU3V6B-HF寄存器類型

① “線網類型”是英文net type的譯稱。

② “寄存器類型”是英文register tvpe的譯稱。

硬件描述語言Verog HDL基礎,寄存器類型表示一個抽象的數據存儲單元,它具有狀態保持作用。寄存器型變量只能在iniual或always內部被賦值。寄存器型變量在沒有被賦值前,它的默認值是x。

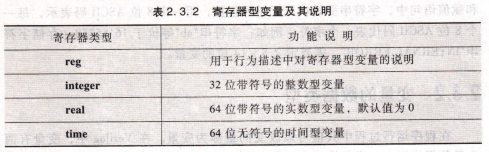

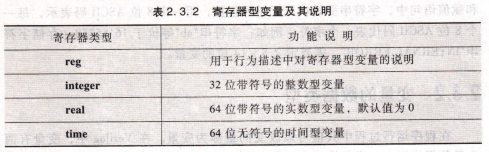

在Verilog中,有4種寄存器類型的變量,如表2.3.2所示。

表2.3,2 寄存器型變量及其說明

常用的寄存器類型由關鍵詞reg定義。如果沒有明確地說明寄存器型變量是多位寬的矢量,則寄存器變量的位寬為1位c reg型變量的定義格式如下:

reg[n-1:0] 變量名1,變量名2,…,變量名n;

下面是reg型變量定義的一些例子:

reg clock;//定義1位寄存器變量

reg[3:0] counter;//定義4位寄存器變量

integer、real和time等3種寄存器型變量都是純數學的抽象描述,不對應任何具體的硬件電路。integer型變量通常用于對整數型常量進行存儲和運算,在算術運算中integer型數據被視為有符號的數,用二進制補碼的形式存儲。而reg型數據通常被當作無符號數來處理。每個integer型變量存儲一個至少32位的整數值。注意integer型變量不能使用位矢量,例如integer[3:0]num;的定義是錯誤的。integer型變量的應用舉例如下:

integer counter;//定義一個整型變量counter

initial

counter=-1;//將一1以補碼的形式存儲在counter中

其中,inidal是一種過程語句結構,只有寄存器類型的變量才能在inITial內部被賦值。

rea1型變量通常用于對實數型常量進行存儲和運算,實數不能定義范圍,其默認值為0。當實數值被賦給一個Integer型變量時,只保留整數部分的值,小數點后面的值被截掉。real型變量的應用舉例如下:

real delta;//定義一個實數型變量delta

initial

begin

邏輯代數與硬件描述語言基礎,寄存器類型,功能說明reg,用于行為描述中對寄存器型變量的說明integer,32位帶符號的整數型變量real,64位帶符號的實數型變量,默認值為0,time,64位無符號的時間型變量.

ZRU3V6B-HF寄存器類型

① “線網類型”是英文net type的譯稱。

② “寄存器類型”是英文register tvpe的譯稱。

硬件描述語言Verog HDL基礎,寄存器類型表示一個抽象的數據存儲單元,它具有狀態保持作用。寄存器型變量只能在iniual或always內部被賦值。寄存器型變量在沒有被賦值前,它的默認值是x。

在Verilog中,有4種寄存器類型的變量,如表2.3.2所示。

表2.3,2 寄存器型變量及其說明

常用的寄存器類型由關鍵詞reg定義。如果沒有明確地說明寄存器型變量是多位寬的矢量,則寄存器變量的位寬為1位c reg型變量的定義格式如下:

reg[n-1:0] 變量名1,變量名2,…,變量名n;

下面是reg型變量定義的一些例子:

reg clock;//定義1位寄存器變量

reg[3:0] counter;//定義4位寄存器變量

integer、real和time等3種寄存器型變量都是純數學的抽象描述,不對應任何具體的硬件電路。integer型變量通常用于對整數型常量進行存儲和運算,在算術運算中integer型數據被視為有符號的數,用二進制補碼的形式存儲。而reg型數據通常被當作無符號數來處理。每個integer型變量存儲一個至少32位的整數值。注意integer型變量不能使用位矢量,例如integer[3:0]num;的定義是錯誤的。integer型變量的應用舉例如下:

integer counter;//定義一個整型變量counter

initial

counter=-1;//將一1以補碼的形式存儲在counter中

其中,inidal是一種過程語句結構,只有寄存器類型的變量才能在inITial內部被賦值。

rea1型變量通常用于對實數型常量進行存儲和運算,實數不能定義范圍,其默認值為0。當實數值被賦給一個Integer型變量時,只保留整數部分的值,小數點后面的值被截掉。real型變量的應用舉例如下:

real delta;//定義一個實數型變量delta

initial

begin

邏輯代數與硬件描述語言基礎,寄存器類型,功能說明reg,用于行為描述中對寄存器型變量的說明integer,32位帶符號的整數型變量real,64位帶符號的實數型變量,默認值為0,time,64位無符號的時間型變量.

公網安備44030402000607

公網安備44030402000607