ADC-811MC移位寄存器

發布時間:2019/10/14 18:31:26 訪問次數:2190

ADC-811MC如前所述,D鎖存器在使能信號E為邏輯1期間更新狀態,在圖5.3.1(a)所示的波形圖中以加粗部分表示這個敏感時段。在這期間,它的輸出會隨輸人信號變化,從而使很多時序邏輯功能不能實現,例如6.5節中將要討論的移位寄存器和計數器。實現這些功能要求存儲電路對時鐘信號的某一邊沿敏感,而在其他時刻保持狀態不變,不受輸人信號變化的影響。這種在時鐘脈沖邊沿作用下的狀態刷新稱為觸發,具有這種特性的存儲單元電路稱為觸發器。不同電路 E結構的觸發器對時鐘脈沖的敏感邊沿可能不同,分為上升沿觸發和下降沿觸發。本書以

CP①命名上升沿觸發的時鐘信號,觸發邊沿如圖5.3.1(b)波形中的箭頭所示;以CP命名下降沿觸發的時鐘信號,觸發邊沿如圖5.3.1(c)中的箭頭所示。

在Venlog中,對脈沖電平敏感的鎖存器和脈沖邊沿敏感的觸發器的描述語句是不同的,這一點將在5.5節中說明.正因為如此, 能或時鐘信號的不同響應.這里要特別強調鎖存器與觸發器在概念上的(a)對高電平敏感(響應)差異.(b)對上升沿敏感(c)對下降沿敏感.

目前應用的觸發器主要有三種電路結構:主從觸發器、維持阻塞觸發器和利用傳輸延遲的觸發器。下面分別予以討論。

工作原理

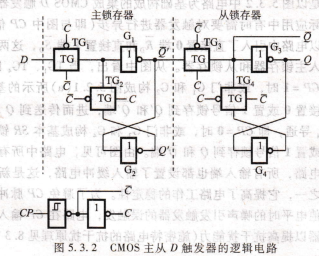

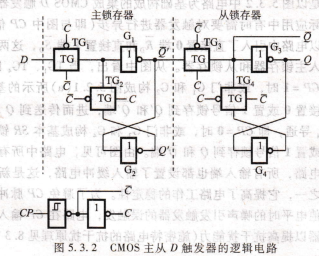

將兩個圖5.2.11(a)所示的D鎖存器級聯,則構成CMOs主從觸發器①,如圖5.3,2所示。圖中左邊的鎖存器稱為主鎖存器,右邊的稱為從鎖存器。主鎖存器的鎖存使能信號正好與從鎖存器反相,利用兩個鎖存器的交互鎖存,則可實現存儲數據和輸入信號之間的隔離。

ADC-811MC如前所述,D鎖存器在使能信號E為邏輯1期間更新狀態,在圖5.3.1(a)所示的波形圖中以加粗部分表示這個敏感時段。在這期間,它的輸出會隨輸人信號變化,從而使很多時序邏輯功能不能實現,例如6.5節中將要討論的移位寄存器和計數器。實現這些功能要求存儲電路對時鐘信號的某一邊沿敏感,而在其他時刻保持狀態不變,不受輸人信號變化的影響。這種在時鐘脈沖邊沿作用下的狀態刷新稱為觸發,具有這種特性的存儲單元電路稱為觸發器。不同電路 E結構的觸發器對時鐘脈沖的敏感邊沿可能不同,分為上升沿觸發和下降沿觸發。本書以

CP①命名上升沿觸發的時鐘信號,觸發邊沿如圖5.3.1(b)波形中的箭頭所示;以CP命名下降沿觸發的時鐘信號,觸發邊沿如圖5.3.1(c)中的箭頭所示。

在Venlog中,對脈沖電平敏感的鎖存器和脈沖邊沿敏感的觸發器的描述語句是不同的,這一點將在5.5節中說明.正因為如此, 能或時鐘信號的不同響應.這里要特別強調鎖存器與觸發器在概念上的(a)對高電平敏感(響應)差異.(b)對上升沿敏感(c)對下降沿敏感.

目前應用的觸發器主要有三種電路結構:主從觸發器、維持阻塞觸發器和利用傳輸延遲的觸發器。下面分別予以討論。

工作原理

將兩個圖5.2.11(a)所示的D鎖存器級聯,則構成CMOs主從觸發器①,如圖5.3,2所示。圖中左邊的鎖存器稱為主鎖存器,右邊的稱為從鎖存器。主鎖存器的鎖存使能信號正好與從鎖存器反相,利用兩個鎖存器的交互鎖存,則可實現存儲數據和輸入信號之間的隔離。

公網安備44030402000607

公網安備44030402000607