抗輻射加固邏輯芯片的兩倍以上實現對雙口RAM控制器的功能

發布時間:2023/5/9 9:00:31 訪問次數:58

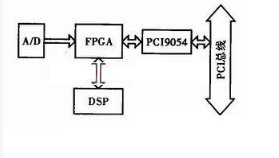

PCI9054與本地總線之間的接口稱之為LOCAL BUS,是CPCI總線系統設計中十分重要的一環。PCI9054 LOCAL BUS在系統設計中,其總線直接與Alter公司的EP2S90F78014芯片的數據總線相連,同時通過運用Verilog HDL語言編程來實現對雙口RAM控制器的功能。

PCI9054 LOCAL BUS有3種工作模式,分別為M、J和C模式。M模式是專為Motorola公司開發和設計的,而另外兩種工作模式就應用的比較廣泛。其中J模式因為沒有LocaL Master,所以它的地址總線和數據線沒有分開,從而增加了開發難度。而在C模式下,PCI9054芯片通過片內的邏輯控制可以將CPCI的局部地址和數據總線分開,從而有效地降低了開發難度,并且能靈活地為本地工作時序提供各種工作方式,設計方案選擇了LOCAL總線的C工作模式,工作頻率為40 MHz。

福建芯鴻科技有限公司http://xhkjgs.51dzw.com

QML-V標準認證的RHFOSC04 (SMD 5962F20207)晶振驅動器/分頻器芯片和RHFAHC00 (SMD 5962F18202)四路NAND門邏輯芯片的門工作速度是典型抗輻射加固邏輯芯片的兩倍以上,保證高頻電路響應速度更快。

采用意法半導體專有的經過整個航天工業檢驗的130nm CMOS技術設計,新器件兼備高工作速度、低工作電流和業內一流的高達 300 krad (Si) TID的RHA(抗輻射加固保證)級別的抗輻射能力,在125 MeV.cm2/mg下無SEL 和 SET[3]現象發生。

其1.8V至3.6V的電源電壓有助于滿足典型衛星和太空飛行器機載設備對功耗和能耗的嚴格限制。

RHFOSC04兼有多個分立邏輯器件的作用,可直接驅動晶體振蕩器,簡化時鐘電路設計并提高電路穩定性,同時節省電路板空間,并提高系統可靠性。分頻器提供標稱頻率、2分頻、4分頻和8分頻輸出,增加了時鐘分頻的靈活性。

新器件交付方式有裸片和封裝芯片兩種,裸片可以直接集成在客戶應用設計的系統級封裝(SiP)內,封裝芯片采用陶瓷密封Flat 14 (RHFAHC00)和Flat 10 (RHFOSC04)。

PCI9054支持主模式、從模式和DMA傳輸方式,根據本系統設計的需求,采用從模式傳輸方式,即允許CPCI總線上的主設備訪問局部總線上的配置寄存器或內存,支持多種模式傳輸。

FPGA內部邏輯要設計本地端總線控制模塊,實現局部總線的狀態控制,同時產生片內的讀寫時序及地址信號以支持突發傳輸和單周期傳輸,因此使用Verilog HDL語言中的狀態機來完成上述功能。其狀態轉換。

以PCI9054為核心介紹了CPCI板卡與嵌入式CPU板卡之間高速數據通信系統接口的軟硬件設計。PCI9054因其靈活和方便的接口功能,使操作者只需關心LOCAL BUS接口電路的時序設計,并且利用其傳輸速率高的特性,對實時性要求較高的系統解決其傳輸數據的問題。

(素材:21ic.如涉版權請聯系刪除)

PCI9054與本地總線之間的接口稱之為LOCAL BUS,是CPCI總線系統設計中十分重要的一環。PCI9054 LOCAL BUS在系統設計中,其總線直接與Alter公司的EP2S90F78014芯片的數據總線相連,同時通過運用Verilog HDL語言編程來實現對雙口RAM控制器的功能。

PCI9054 LOCAL BUS有3種工作模式,分別為M、J和C模式。M模式是專為Motorola公司開發和設計的,而另外兩種工作模式就應用的比較廣泛。其中J模式因為沒有LocaL Master,所以它的地址總線和數據線沒有分開,從而增加了開發難度。而在C模式下,PCI9054芯片通過片內的邏輯控制可以將CPCI的局部地址和數據總線分開,從而有效地降低了開發難度,并且能靈活地為本地工作時序提供各種工作方式,設計方案選擇了LOCAL總線的C工作模式,工作頻率為40 MHz。

福建芯鴻科技有限公司http://xhkjgs.51dzw.com

QML-V標準認證的RHFOSC04 (SMD 5962F20207)晶振驅動器/分頻器芯片和RHFAHC00 (SMD 5962F18202)四路NAND門邏輯芯片的門工作速度是典型抗輻射加固邏輯芯片的兩倍以上,保證高頻電路響應速度更快。

采用意法半導體專有的經過整個航天工業檢驗的130nm CMOS技術設計,新器件兼備高工作速度、低工作電流和業內一流的高達 300 krad (Si) TID的RHA(抗輻射加固保證)級別的抗輻射能力,在125 MeV.cm2/mg下無SEL 和 SET[3]現象發生。

其1.8V至3.6V的電源電壓有助于滿足典型衛星和太空飛行器機載設備對功耗和能耗的嚴格限制。

RHFOSC04兼有多個分立邏輯器件的作用,可直接驅動晶體振蕩器,簡化時鐘電路設計并提高電路穩定性,同時節省電路板空間,并提高系統可靠性。分頻器提供標稱頻率、2分頻、4分頻和8分頻輸出,增加了時鐘分頻的靈活性。

新器件交付方式有裸片和封裝芯片兩種,裸片可以直接集成在客戶應用設計的系統級封裝(SiP)內,封裝芯片采用陶瓷密封Flat 14 (RHFAHC00)和Flat 10 (RHFOSC04)。

PCI9054支持主模式、從模式和DMA傳輸方式,根據本系統設計的需求,采用從模式傳輸方式,即允許CPCI總線上的主設備訪問局部總線上的配置寄存器或內存,支持多種模式傳輸。

FPGA內部邏輯要設計本地端總線控制模塊,實現局部總線的狀態控制,同時產生片內的讀寫時序及地址信號以支持突發傳輸和單周期傳輸,因此使用Verilog HDL語言中的狀態機來完成上述功能。其狀態轉換。

以PCI9054為核心介紹了CPCI板卡與嵌入式CPU板卡之間高速數據通信系統接口的軟硬件設計。PCI9054因其靈活和方便的接口功能,使操作者只需關心LOCAL BUS接口電路的時序設計,并且利用其傳輸速率高的特性,對實時性要求較高的系統解決其傳輸數據的問題。

(素材:21ic.如涉版權請聯系刪除)

上一篇:扭矩無線傳感器的種類

公網安備44030402000607

公網安備44030402000607