Э”ИлЧиҝ№Іо®җ•юҢ§ЦВХ`ІоtAC•rзҠЙПЙэСШөҪ”ө“юЭ”іцСУ•r

°lІј•rйg:2022/6/3 18:03:42 ФLҶ–ҙО”ө:153

DDR2 SDRAM®aЖ·ФЪЙПлҠК№УГЗ°РиЯMРРіхКј»Ҝ,ІўҢҰДЈКҪјДҙжЖчЈЁMode RegisterЈ©ЯMРРЕдЦГ,ҙ_¶ЁЛщРиТӘөДН»°lйL¶ИЈЁBurst LengthЈ©ЎўН»°lоҗРНЈЁBurst TypeЈ©,CAS СУ•rөИЎЈ

Ҫ»Бч…ў”өұнХчөДКЗРҫЖ¬өД№ӨЧчРФДЬЈ¬Т»°гУГЛСЛч·ЁҒнңyФҮҪ»Бч…ў”ө,ФЪMagnum 2ңyФҮПөҪyЙПңyФҮtAC…ў”өһйАэҒнҪйҪBңyФҮҷCИзәОЯMРРҪ»Бч…ў”өөДңyФҮЈ¬tAC•rзҠЙПЙэСШөҪ”ө“юЭ”іцСУ•rЈЁAddress to Output DelayЈ©Ј¬Ф“…ў”өФҪРЎ„t®aЖ·н‘‘ӘЛЩ¶ИФҪҝмЎЈ

ЛСЛч·ЁөДҫЯуwЛјВ·һйјЩФOt0•rҝМөШЦ·УРР§Ј¬лSәуФЪt0+tSTEPЯMРРЧx”ө“юЈ¬Из№ыЧxИЎіЙ№ҰЈ¬„ttAC=t0+tSTEPЈ¬Из№ыЧxИЎК§”Ў„tФЪt0+2tSTEP•rЧxИЎ”ө“юЈ¬ИзҙЛСӯӯhЦұөҪЧxИЎіЙ№ҰһйЦ№ЎЈ

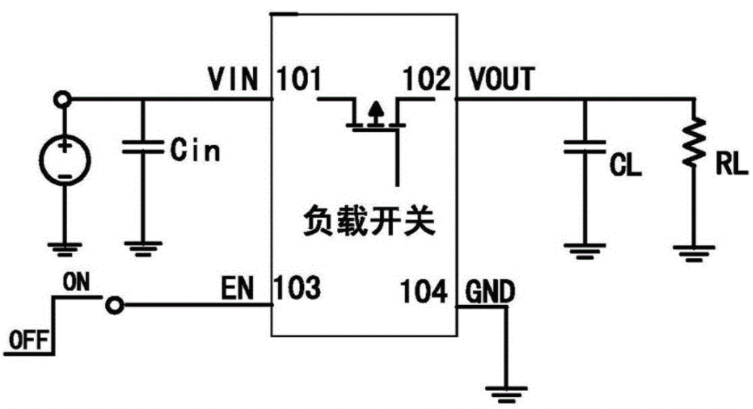

®”»¬„Уҙ°кPЙП•r,ҝЙУГІЩҝvКЦұъІЩҝvҙ°ЙПөДжiйVІеИЛҙ°ҝтҝЧЦР¶шжiЧЎЎЈСbФЪ»¬ЭҶЬүөАғИөДғЙӮҖжiЦщУГҒнжiЧЎІЩҝvКЦұъ,Т»ӮҖФЪҙ°‘фИ«й_•rК№УГ,БнТ»ӮҖФЪҙ°‘фИ«кP•rК№УГЎЈ

й_ҙ°•r,үәПВІЩҝvКЦұъЙПөДЛЙй_дN,ПИПтАпФЩПтәуАӯІЩҝvКЦұъ,ҫНҝЙК№жiйlҸДҙ°ҝтҝЧЦРійіц,ІўК№ҙ°‘фСШЬүөАПтә󻬄Ӷшҙтй_,ЦұөҪКЦұъЕcәуГжөДТ»ӮҖжiЦщЭ^әПһйЦ№ЎЈ

ФЪҫoјұЗйӣrПВ,ҝЙҢўФ“ҙ°ИЎПВ,іЙһйҷCҪMИЛҶTөД‘ӘјұіцҝЪcИЎПВФ“ҙ°өД·Ҫ·ЁКЗ:ПИҢўЮD„УұЫЙПөД°ЧЙ«ҳЛУӣЕcЎ°ҙ°‘ф’Ғ—үЎұҳЛЕЖЙПөДҳЛУӣҢҰэR,И»әуійіцҝмР¶дN,ФЩПтПВАӯ’Ғ—үКЦұъ,К№ЙПқLЧУГ“лxЬүөА,јҙҝЙИЎПВЎЈ

ФЪҝШЦЖЖчТ»¶Л(MCUЎўFPGAЎўDSP)К№УГәҶҶОөДРЈңКПө”өЎЈө«КЗЈ¬Я@ҳУУРғЙҙуИұьcЈәРиТӘо~НвөДҝШЦЖЖчЩYФҙЈ¬ТФј°ЖчјюЕcЖчјюЦ®йgөДЭ”ИлЧиҝ№Іо®җ•юҢ§ЦВХ`ІоЎЈ

һйБЛп@КҫЕcәу¶ЛРЈңКПаұИЈ¬Ж¬ғИРЈңКЛщҫЯӮдөДғһ„ЭЈ¬ОТӮғңyБҝБЛТ»ПөБРAD7606C-18СbЦГ(,ФЪңyБҝ•rЈ¬јЩФOЭ”ИлЧиҝ№КјҪKһйөдРНЦө(RIN=1.2MҰё)ЎЈ

ЕcЖ¬ғИРЈңКПажЗГАЎЈЯ@ТвО¶ЦшЛьөДҢҚлHЭ”ИлЧиҝ№(RIN)·ЗіЈҪУҪьөдРНЦө,ҢҚлHЭ”ИлЧиҝ№(RIN)ЙФОўёЯУЪөдРНЦө,Ж¬ғИРЈңКұЈіЦЛщУРСbЦГәНRFILTERЦөөДҝӮХ`ІоҫщөНУЪ0.03%ЎЈ

DDR2 SDRAM®aЖ·ФЪЙПлҠК№УГЗ°РиЯMРРіхКј»Ҝ,ІўҢҰДЈКҪјДҙжЖчЈЁMode RegisterЈ©ЯMРРЕдЦГ,ҙ_¶ЁЛщРиТӘөДН»°lйL¶ИЈЁBurst LengthЈ©ЎўН»°lоҗРНЈЁBurst TypeЈ©,CAS СУ•rөИЎЈ

Ҫ»Бч…ў”өұнХчөДКЗРҫЖ¬өД№ӨЧчРФДЬЈ¬Т»°гУГЛСЛч·ЁҒнңyФҮҪ»Бч…ў”ө,ФЪMagnum 2ңyФҮПөҪyЙПңyФҮtAC…ў”өһйАэҒнҪйҪBңyФҮҷCИзәОЯMРРҪ»Бч…ў”өөДңyФҮЈ¬tAC•rзҠЙПЙэСШөҪ”ө“юЭ”іцСУ•rЈЁAddress to Output DelayЈ©Ј¬Ф“…ў”өФҪРЎ„t®aЖ·н‘‘ӘЛЩ¶ИФҪҝмЎЈ

ЛСЛч·ЁөДҫЯуwЛјВ·һйјЩФOt0•rҝМөШЦ·УРР§Ј¬лSәуФЪt0+tSTEPЯMРРЧx”ө“юЈ¬Из№ыЧxИЎіЙ№ҰЈ¬„ttAC=t0+tSTEPЈ¬Из№ыЧxИЎК§”Ў„tФЪt0+2tSTEP•rЧxИЎ”ө“юЈ¬ИзҙЛСӯӯhЦұөҪЧxИЎіЙ№ҰһйЦ№ЎЈ

®”»¬„Уҙ°кPЙП•r,ҝЙУГІЩҝvКЦұъІЩҝvҙ°ЙПөДжiйVІеИЛҙ°ҝтҝЧЦР¶шжiЧЎЎЈСbФЪ»¬ЭҶЬүөАғИөДғЙӮҖжiЦщУГҒнжiЧЎІЩҝvКЦұъ,Т»ӮҖФЪҙ°‘фИ«й_•rК№УГ,БнТ»ӮҖФЪҙ°‘фИ«кP•rК№УГЎЈ

й_ҙ°•r,үәПВІЩҝvКЦұъЙПөДЛЙй_дN,ПИПтАпФЩПтәуАӯІЩҝvКЦұъ,ҫНҝЙК№жiйlҸДҙ°ҝтҝЧЦРійіц,ІўК№ҙ°‘фСШЬүөАПтә󻬄Ӷшҙтй_,ЦұөҪКЦұъЕcәуГжөДТ»ӮҖжiЦщЭ^әПһйЦ№ЎЈ

ФЪҫoјұЗйӣrПВ,ҝЙҢўФ“ҙ°ИЎПВ,іЙһйҷCҪMИЛҶTөД‘ӘјұіцҝЪcИЎПВФ“ҙ°өД·Ҫ·ЁКЗ:ПИҢўЮD„УұЫЙПөД°ЧЙ«ҳЛУӣЕcЎ°ҙ°‘ф’Ғ—үЎұҳЛЕЖЙПөДҳЛУӣҢҰэR,И»әуійіцҝмР¶дN,ФЩПтПВАӯ’Ғ—үКЦұъ,К№ЙПқLЧУГ“лxЬүөА,јҙҝЙИЎПВЎЈ

ФЪҝШЦЖЖчТ»¶Л(MCUЎўFPGAЎўDSP)К№УГәҶҶОөДРЈңКПө”өЎЈө«КЗЈ¬Я@ҳУУРғЙҙуИұьcЈәРиТӘо~НвөДҝШЦЖЖчЩYФҙЈ¬ТФј°ЖчјюЕcЖчјюЦ®йgөДЭ”ИлЧиҝ№Іо®җ•юҢ§ЦВХ`ІоЎЈ

һйБЛп@КҫЕcәу¶ЛРЈңКПаұИЈ¬Ж¬ғИРЈңКЛщҫЯӮдөДғһ„ЭЈ¬ОТӮғңyБҝБЛТ»ПөБРAD7606C-18СbЦГ(,ФЪңyБҝ•rЈ¬јЩФOЭ”ИлЧиҝ№КјҪKһйөдРНЦө(RIN=1.2MҰё)ЎЈ

ЕcЖ¬ғИРЈңКПажЗГАЎЈЯ@ТвО¶ЦшЛьөДҢҚлHЭ”ИлЧиҝ№(RIN)·ЗіЈҪУҪьөдРНЦө,ҢҚлHЭ”ИлЧиҝ№(RIN)ЙФОўёЯУЪөдРНЦө,Ж¬ғИРЈңКұЈіЦЛщУРСbЦГәНRFILTERЦөөДҝӮХ`ІоҫщөНУЪ0.03%ЎЈ

ҹбйTьc“ф

ҹбйTьc“ф

- ”өЧЦһVІЁЖчУІјюјУЛЩТэЗжҳOҙуМбЙэFFTәНFIR

- ЛДлҠЖҪГ}ӣ_·щ¶ИХ{ЦЖКЗPCIe 6.0ҝЛ·юНЁөА

- ХыӮҖјЬҳӢГжПтSOA¶ЁБxМбЙэРҫЖ¬ЦЖФмДЬБҰәНҝЙҝҝ

- DPDоlЧVІўТэУГаҸөАР№В©ұИ(ACLR)”өЧЦУЙ

- FРНGРНәНHРНҳЛңКГЬ¶ИЯBҪУҪУҫҖүKПаЭ^ӮчҪyMC

- лpБРЦұІеКҪ·вСb(DIP)»тХЯұнГжЩNСbЖчјю(S

- ҝШЦЖЖчөДГҝӮҖҶОӘҡөДADC”ө“юьcҲМРРәуМҺАнФцјУ

- ғИәЛөД32О»өН№ҰәДMCUРҫЖ¬өН№ҰәДОпВ“ҫWНЁРЕ

- Э”іцлҠүәФOЦГәН•rРтҝШЦЖФOЦГRAWУтМҺАнөДҹo“p

- ІўРРЧЦөД•rзҠЛЩВККХ°lҙ®РР”ө“юADCК§Х{Х`ІоөД

НЖЛ]јјРgЩYБП

НЖЛ]јјРgЩYБП

- оlЧVғxөДҪвХ{№ҰДЬ

- ¬FҙъоlЧVғxФЪёъЫҷФҙДЈКҪПВТІҝЙТФК№УГMakerәНЎчMak... [Ф”јҡ]

- ДЈ”MәН»мәПРЕМ–ЖҪЕ_TreoФ”Зй

- PXIәНLXIДЈүK»ҜҪвӣQ·Ҫ°ёҪвЧx

- AN-13-0004_CANКХ°lЖчҪYҳӢ…ў”өМШ

- ЖБұО–ЕІЫңПјјРg (SGT)&#

- өЪТ»ҙъSGT MOSFETПөБРјјРgҪYҳӢ…ў”ө·в

- И«ЗтКЧоwGSE DPUРҫЖ¬°lІј

- ¶аГҪуw…fМҺАнЖчSM501ФЪЗ¶ИлКҪПөҪyЦРөД‘ӘУГ

- »щУЪIEEE802.11bөДEPAңШ¶ИЧғЛНЖч

- QUICCEngineРВТэЗжНЖ„УIPҫWҪjёпРВ

- SoCГжКА°ЛДкәуөД®aҳIҷCУц

- MPC8xxПөБРМҺАнЖчөДЗ¶ИлКҪПөҪyлҠФҙФOУӢ

- dsPICј°ЖдФЪҪ»БчЧғоlХ{ЛЩЦРөД‘ӘУГСРҫҝ

№«ҫW°ІӮд44030402000607

№«ҫW°ІӮд44030402000607