將運放兩個輸入端連接到差分信號兩個輸出端消除共模噪聲的影響

發布時間:2024/8/6 9:01:57 訪問次數:170

差分輸入方式是一種有效降低運放噪聲的方法。在LT1028運放的設計中,可以采用差分輸入方式來降低輸入端的共模噪聲。

具體來說,可以將運放的兩個輸入端分別連接到差分信號的兩個輸出端,從而消除共模噪聲的影響。需要注意的是,在采用差分輸入方式時,應確保差分信號的平衡性和對稱性,以避免引入額外的噪聲。

此外,還應注意電阻和電容的布局和布線方式,以避免引入額外的噪聲。

REFOUT提供1.23V內部生成的基準電壓源。在通道寄存器的控制下,每個DAC的基準輸入(稱為V偏見)在內部基準源、REFIN端子(用于外部基準)和電源電壓(V(DD/)2)的一半之間多路復用。

選擇的電壓,V偏見,提供單電源電路中雙極性信號所需的失調“零”;DAC針對1.875V的輸出范圍進行縮放偏見.該表顯示了二進制補碼編碼沿傳遞函數的重要點。

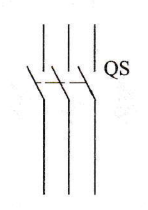

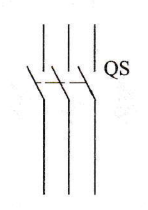

絕大多數的模擬電路設計者都知道怎么在雙電源電壓的條件下使用運算放大器,比如圖一左邊的那個電路,一個雙電源是由一個正電源和一個相等電壓的負電源組成。

有一些新的運放有兩個不同的最高輸出電壓和最低輸出電壓。這種運放的數據手冊中會特別分別指明Voh 和Vol 。

http://jhbdt1.51dzw.com深圳市俊暉半導體有限公司

差分輸入方式是一種有效降低運放噪聲的方法。在LT1028運放的設計中,可以采用差分輸入方式來降低輸入端的共模噪聲。

具體來說,可以將運放的兩個輸入端分別連接到差分信號的兩個輸出端,從而消除共模噪聲的影響。需要注意的是,在采用差分輸入方式時,應確保差分信號的平衡性和對稱性,以避免引入額外的噪聲。

此外,還應注意電阻和電容的布局和布線方式,以避免引入額外的噪聲。

REFOUT提供1.23V內部生成的基準電壓源。在通道寄存器的控制下,每個DAC的基準輸入(稱為V偏見)在內部基準源、REFIN端子(用于外部基準)和電源電壓(V(DD/)2)的一半之間多路復用。

選擇的電壓,V偏見,提供單電源電路中雙極性信號所需的失調“零”;DAC針對1.875V的輸出范圍進行縮放偏見.該表顯示了二進制補碼編碼沿傳遞函數的重要點。

絕大多數的模擬電路設計者都知道怎么在雙電源電壓的條件下使用運算放大器,比如圖一左邊的那個電路,一個雙電源是由一個正電源和一個相等電壓的負電源組成。

有一些新的運放有兩個不同的最高輸出電壓和最低輸出電壓。這種運放的數據手冊中會特別分別指明Voh 和Vol 。

http://jhbdt1.51dzw.com深圳市俊暉半導體有限公司

公網安備44030402000607

公網安備44030402000607