三維集成電路

發布時間:2011/8/25 10:06:33 訪問次數:3435

1. 3D IC與摩爾定律

三維集成電路(3D IC)又稱立體集成電路,本質上說仍然屬于傳統的以硅材料為主的半導體集成電路,并不是一種新型的集成電路品種,只是一種新的封裝形式。

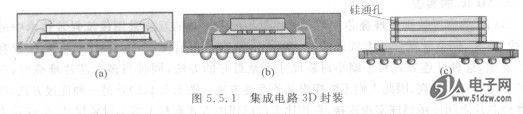

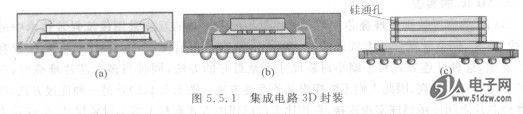

傳統的集成電路封裝是在一個封裝內放置一個晶片(裸芯片)或平面放置多個晶片(MCM),這種封裝形式稱為2D,即晶片在XY二維平面分布。而3D IC則是將多個晶片堆疊放置,如圖5.5.1所示,從而捉高了封裝效率(封裝效率≥100%),對于集成電路產品而言則是提高了集成度和性能。

隨著半導體工藝特征尺寸的不斷縮小,特別是進入納米尺寸范圍(小于0.1μm即100nm)后,半導體制造技術難度越來越大。傳統的技術越來越接近物理尺寸極限,而新的技術一時還難以接替,因而摩爾定律難以為繼的預言已經多次提出,只是由于科技界不懈的努力使傳統半導體技術得以延續,90nm.65nm、45nm.32nm、22nm、…實際上,不可否認的是如果近年來半導體技術不能有重大突破,摩爾定律難免壽終正寢。

正是3D IC,這個在半導體領域被視為技術含量不高的封裝技術上的新進展,使傳統半導體技術出現新的契機,利用封裝技術提高集成度,繼續電子信息產品微小型化、多功能化和智能化的進程,從而使瀕臨失效的摩爾定律暫時得以延續,因而受到業界高度重視,成為電子制造領域的熱門技術,并且對電子產品發展產生重大影響。

2. 3D lC的特點

1)縮小封裝尺寸

與同樣數量晶片的2D封裝比,3D IC最直觀的優點就是可以大幅縮小封裝的平面尺寸,提高芯片的晶體管密度。3D封裝增加了最終封裝的高度,但在電路板的各種元器件中,IC的高度不是問題,一般電解電容、連接器都比較高(大于3~5mm),目前一個晶片厚度約0. 2mm,在3D封裝中經過減厚可達0.Imm或更薄。

2)提高互連效率

在傳統的集成電路技術中,作為互連層的金屬位于2D有源電路上方,互連的基本挑戰是互連造成的傳輸延遲,特別隨著高速電路的應用,延遲問題就更為突出。為了避免這種延遲,同時也為了滿足性能、頻寬和功耗的要求,采用垂直方向上將芯片盞層的新技術,可以縮短互連線(見圖5.5.2),實現高效互連,從而提升芯片運行速度。

3)降低芯片的功耗

3D架構使互連線縮短不僅有利于信號傳輸,而且可以降低芯片的功耗。隨著數字電路開關速度的提高,在互連線上消耗的功率相當驚人。據統計,在一種高工作頻率的數字集成電路中,90%以上的功率實際上是由10%的長互連線消耗的。減小互連線長度,不僅會提高電路速度,還會有效地降低電路的功耗。

4)較低的成本

與單芯片系統SoC相比,3D IC系統封裝電路的開發難度低、周期短,因而可以降低研發成本。

另一方面,對于復雜系統來說,在設計階段導人3D IC的概念,可以將一個完整、復雜的芯片,拆分成若干子功效芯片、在不同層實現,既增強了芯片功能,又避免了相關的成本、設計復雜度增加等問題。

當然,3D IC也不全是優點。其主要缺點是:如果堆疊中的一層集成電路出現問題,所有堆疊的裸片都將失效;此外,封裝技術難度的提高也會增加一部分成本。

3. 3D IC的實現

3D IC的實現關鍵是堆疊芯片的互連。早期的芯片間的互連采用傳統封裝技術中的“打線”方式,即金絲球焊的方式來完成,如圖5.5.1(a)所示,由于技術成熟,實現比較容易。顯然,這種互連方式對于縮小封裝尺寸不是最好的方法,同時當多個芯片堆疊時,對

金絲球焊的要求提高,因此人們不斷探索其他互連方法。圖5.5.1(b)是另一種連接方式,即在堆疊芯片之間使用焊球實現連接,它相比金絲球焊的方式有利于縮小封裝尺寸,但這種方式對于3層以上堆疊,例如要實現第一層與第三層的連接就比較困難。目前最受推崇的連接技術是所謂硅通孔(TSV)技術,如圖5.5.1(c)所示,有關TSV將在下面單獨介紹。

4. 3D IC的應用

目前3D IC已經逐步進入實用階段,首先在部分高端電子產品中,例如基于TSV的微機電系統( MEMS)和影像傳感器(CMOS)等產品中得到應用。未來可擴展至DSP.NAND Flash、DRAM、RF和通信IC等產品領域,進而延伸至繪圖芯片、多核處理器、電源供應器和功率放大器、FPGA等芯片產品領域。同時各種邏輯組件、傳感器、模擬組件、射頻、徽處理器等堆疊構成的多功能系統芯片也將成為3D IC的主要發展方向。據有關機構預測,未來3D芯片的年均復合增長率將超過60%,在半導體市場的比重將持續上升。 QMV50ADA

1. 3D IC與摩爾定律

三維集成電路(3D IC)又稱立體集成電路,本質上說仍然屬于傳統的以硅材料為主的半導體集成電路,并不是一種新型的集成電路品種,只是一種新的封裝形式。

傳統的集成電路封裝是在一個封裝內放置一個晶片(裸芯片)或平面放置多個晶片(MCM),這種封裝形式稱為2D,即晶片在XY二維平面分布。而3D IC則是將多個晶片堆疊放置,如圖5.5.1所示,從而捉高了封裝效率(封裝效率≥100%),對于集成電路產品而言則是提高了集成度和性能。

隨著半導體工藝特征尺寸的不斷縮小,特別是進入納米尺寸范圍(小于0.1μm即100nm)后,半導體制造技術難度越來越大。傳統的技術越來越接近物理尺寸極限,而新的技術一時還難以接替,因而摩爾定律難以為繼的預言已經多次提出,只是由于科技界不懈的努力使傳統半導體技術得以延續,90nm.65nm、45nm.32nm、22nm、…實際上,不可否認的是如果近年來半導體技術不能有重大突破,摩爾定律難免壽終正寢。

正是3D IC,這個在半導體領域被視為技術含量不高的封裝技術上的新進展,使傳統半導體技術出現新的契機,利用封裝技術提高集成度,繼續電子信息產品微小型化、多功能化和智能化的進程,從而使瀕臨失效的摩爾定律暫時得以延續,因而受到業界高度重視,成為電子制造領域的熱門技術,并且對電子產品發展產生重大影響。

2. 3D lC的特點

1)縮小封裝尺寸

與同樣數量晶片的2D封裝比,3D IC最直觀的優點就是可以大幅縮小封裝的平面尺寸,提高芯片的晶體管密度。3D封裝增加了最終封裝的高度,但在電路板的各種元器件中,IC的高度不是問題,一般電解電容、連接器都比較高(大于3~5mm),目前一個晶片厚度約0. 2mm,在3D封裝中經過減厚可達0.Imm或更薄。

2)提高互連效率

在傳統的集成電路技術中,作為互連層的金屬位于2D有源電路上方,互連的基本挑戰是互連造成的傳輸延遲,特別隨著高速電路的應用,延遲問題就更為突出。為了避免這種延遲,同時也為了滿足性能、頻寬和功耗的要求,采用垂直方向上將芯片盞層的新技術,可以縮短互連線(見圖5.5.2),實現高效互連,從而提升芯片運行速度。

3)降低芯片的功耗

3D架構使互連線縮短不僅有利于信號傳輸,而且可以降低芯片的功耗。隨著數字電路開關速度的提高,在互連線上消耗的功率相當驚人。據統計,在一種高工作頻率的數字集成電路中,90%以上的功率實際上是由10%的長互連線消耗的。減小互連線長度,不僅會提高電路速度,還會有效地降低電路的功耗。

4)較低的成本

與單芯片系統SoC相比,3D IC系統封裝電路的開發難度低、周期短,因而可以降低研發成本。

另一方面,對于復雜系統來說,在設計階段導人3D IC的概念,可以將一個完整、復雜的芯片,拆分成若干子功效芯片、在不同層實現,既增強了芯片功能,又避免了相關的成本、設計復雜度增加等問題。

當然,3D IC也不全是優點。其主要缺點是:如果堆疊中的一層集成電路出現問題,所有堆疊的裸片都將失效;此外,封裝技術難度的提高也會增加一部分成本。

3. 3D IC的實現

3D IC的實現關鍵是堆疊芯片的互連。早期的芯片間的互連采用傳統封裝技術中的“打線”方式,即金絲球焊的方式來完成,如圖5.5.1(a)所示,由于技術成熟,實現比較容易。顯然,這種互連方式對于縮小封裝尺寸不是最好的方法,同時當多個芯片堆疊時,對

金絲球焊的要求提高,因此人們不斷探索其他互連方法。圖5.5.1(b)是另一種連接方式,即在堆疊芯片之間使用焊球實現連接,它相比金絲球焊的方式有利于縮小封裝尺寸,但這種方式對于3層以上堆疊,例如要實現第一層與第三層的連接就比較困難。目前最受推崇的連接技術是所謂硅通孔(TSV)技術,如圖5.5.1(c)所示,有關TSV將在下面單獨介紹。

4. 3D IC的應用

目前3D IC已經逐步進入實用階段,首先在部分高端電子產品中,例如基于TSV的微機電系統( MEMS)和影像傳感器(CMOS)等產品中得到應用。未來可擴展至DSP.NAND Flash、DRAM、RF和通信IC等產品領域,進而延伸至繪圖芯片、多核處理器、電源供應器和功率放大器、FPGA等芯片產品領域。同時各種邏輯組件、傳感器、模擬組件、射頻、徽處理器等堆疊構成的多功能系統芯片也將成為3D IC的主要發展方向。據有關機構預測,未來3D芯片的年均復合增長率將超過60%,在半導體市場的比重將持續上升。 QMV50ADA

上一篇:封裝/組裝交融——微組裝簡介

上一篇:SiP技術

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607