多人表決電路設計實驗方案

發布時間:2012/2/6 20:28:44 訪問次數:4512

實驗目的CNW138

(1)掌握組合邏輯電路設計的一般過程。

(2)驗證所設計電路的邏輯功能。

實驗設備

本實驗需要的實驗設備如表2.7.3所列。

實驗原理

表2.7.3實驗設備

┏━━━━┳━━━━━━━━┳━━━━━━┳━━━━┓

┃ 序號 ┃ 設備名稱 ┃ 設備型號 ┃ 數量 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 1 ┃數字邏輯學習機 ┃ ┃ 1臺 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 2 ┃萬用表 ┃ ┃ 1臺 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 3 ┃數字集成塊 ┃ 74LSOO ┃ 2片 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 4 ┃數字集成塊 ┃ 74LS20 ┃ 2片 ┃

┗━━━━┻━━━━━━━━┻━━━━━━┻━━━━┛

1.組合邏輯電路設計步驟

組合邏輯電路設計的一般過程是:

(1)根據任務要求列出邏輯狀態表;

(2)通過邏輯狀態表寫出邏輯式;

(3)通過對邏輯式的化簡(或對卡諾圖的化簡),得出最簡的邏輯式;

(4)由最簡邏輯式畫出邏輯圖;

(5)選擇標準器件實現此邏輯式。

邏輯化簡是組合邏輯設計的關鍵步驟之一。為了使電路結構簡單和使用器件較少,往往要求邏輯表達式盡可能簡化。由于實際使用時要考慮電路的工作速度和穩定可靠等因素,在較復雜的電路中,還要求邏輯清晰易懂,所以最簡設計不一定是最佳的。但一般說來,在保證速度、穩定可靠與邏輯清楚的前提下,盡量使用最少的器件,以降低成本,是對邏輯設計考的基本要求。

2.與非門集成塊74LSOO與74LS20

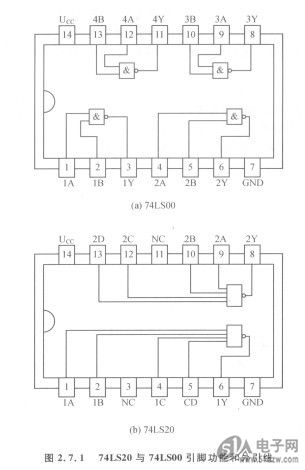

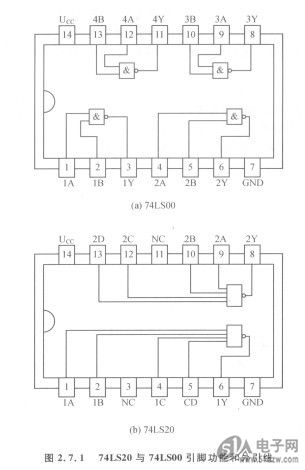

74LSOO為4個雙輸入與非門;74LS20力兩個四輸入端的與非門,一塊芯片中有這樣兩個獨立的與非門,它們的引腳功能和外引線如圖2. 7.1所示。

實驗內容

實驗設計題目:“多人表決電路設計”某項體育比賽A、B、C三個副裁判和一個D主裁判,主裁判的裁定計二票,其他裁判的裁

定計一票,設計一個表決電路,要求在多數票同意得分時電路發出得分信號(≥3票)。

實驗步驟

(1)認真閱讀實驗設計題目,弄清楚題目的要求。

(2)按照組合邏輯電路設計的一般步驟,獨立擬定實驗方案和實驗步驟。

(3)選用設計實驗所需元件(限用與非門來實現)。

(4)按設計搭接電路,進行靜態測試,驗證邏輯功能(自行設計數據記錄表格)。

思考題

(1)組合邏輯電路設計的一般步驟是什么?

(2)為什么要求邏輯表達式盡可能簡化?

(3)為什么說最簡設計不一定是最佳的?

(4) 74LSOO與74LS20都是與非門,它們有什么不同?

(5)本實驗均用74LSOO與非門來實現,要用幾片74LSOO?

實驗目的CNW138

(1)掌握組合邏輯電路設計的一般過程。

(2)驗證所設計電路的邏輯功能。

實驗設備

本實驗需要的實驗設備如表2.7.3所列。

實驗原理

表2.7.3實驗設備

┏━━━━┳━━━━━━━━┳━━━━━━┳━━━━┓

┃ 序號 ┃ 設備名稱 ┃ 設備型號 ┃ 數量 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 1 ┃數字邏輯學習機 ┃ ┃ 1臺 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 2 ┃萬用表 ┃ ┃ 1臺 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 3 ┃數字集成塊 ┃ 74LSOO ┃ 2片 ┃

┣━━━━╋━━━━━━━━╋━━━━━━╋━━━━┫

┃ 4 ┃數字集成塊 ┃ 74LS20 ┃ 2片 ┃

┗━━━━┻━━━━━━━━┻━━━━━━┻━━━━┛

1.組合邏輯電路設計步驟

組合邏輯電路設計的一般過程是:

(1)根據任務要求列出邏輯狀態表;

(2)通過邏輯狀態表寫出邏輯式;

(3)通過對邏輯式的化簡(或對卡諾圖的化簡),得出最簡的邏輯式;

(4)由最簡邏輯式畫出邏輯圖;

(5)選擇標準器件實現此邏輯式。

邏輯化簡是組合邏輯設計的關鍵步驟之一。為了使電路結構簡單和使用器件較少,往往要求邏輯表達式盡可能簡化。由于實際使用時要考慮電路的工作速度和穩定可靠等因素,在較復雜的電路中,還要求邏輯清晰易懂,所以最簡設計不一定是最佳的。但一般說來,在保證速度、穩定可靠與邏輯清楚的前提下,盡量使用最少的器件,以降低成本,是對邏輯設計考的基本要求。

2.與非門集成塊74LSOO與74LS20

74LSOO為4個雙輸入與非門;74LS20力兩個四輸入端的與非門,一塊芯片中有這樣兩個獨立的與非門,它們的引腳功能和外引線如圖2. 7.1所示。

實驗內容

實驗設計題目:“多人表決電路設計”某項體育比賽A、B、C三個副裁判和一個D主裁判,主裁判的裁定計二票,其他裁判的裁

定計一票,設計一個表決電路,要求在多數票同意得分時電路發出得分信號(≥3票)。

實驗步驟

(1)認真閱讀實驗設計題目,弄清楚題目的要求。

(2)按照組合邏輯電路設計的一般步驟,獨立擬定實驗方案和實驗步驟。

(3)選用設計實驗所需元件(限用與非門來實現)。

(4)按設計搭接電路,進行靜態測試,驗證邏輯功能(自行設計數據記錄表格)。

思考題

(1)組合邏輯電路設計的一般步驟是什么?

(2)為什么要求邏輯表達式盡可能簡化?

(3)為什么說最簡設計不一定是最佳的?

(4) 74LSOO與74LS20都是與非門,它們有什么不同?

(5)本實驗均用74LSOO與非門來實現,要用幾片74LSOO?

熱門點擊

熱門點擊

- 集成運放的圖形符號與外形

- 交流信號電阻分壓衰減電路和基準電壓電阻分級電

- 多功能控制器集成電路

- 單聲道OCL音頻功率放大器集成電路故障檢修

- 電容降壓電路

- 二極管限幅電路

- 調諧電平指示器

- 多人表決電路設計實驗方案

- 集成電路圖示音調控制器

- 語筒電路中的RC低頻噪聲切除電路

推薦技術資料

推薦技術資料

- DS2202型示波器試用

- 說起數字示波器,普源算是國內的老牌子了,FQP8N60... [詳細]

公網安備44030402000607

公網安備44030402000607