Blackfin處理器的時鐘頻率控制

發布時間:2012/2/21 19:33:39 訪問次數:2184

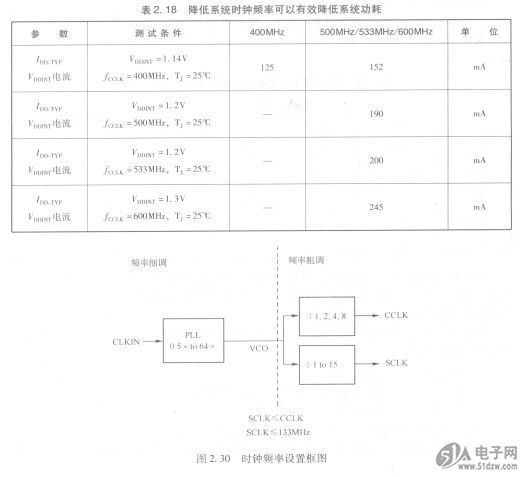

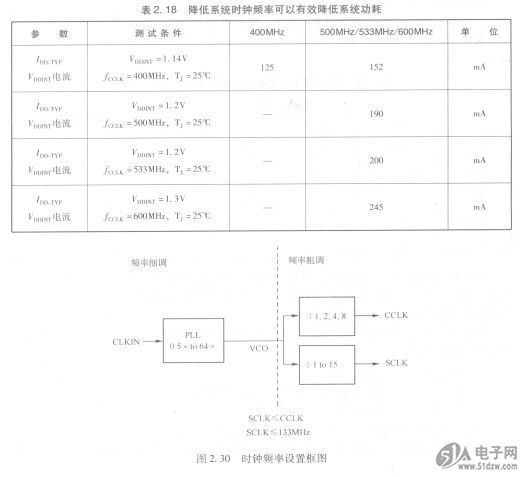

如表2. 18所示,在Blackfin處理器中,降低系統時鐘頻率可以有效降低系統功耗。例如,Blackfin處理器ADSP- BF533通過外部時鐘輸入引腳CLKIN接收外部時鐘源(10~40MHz)的時鐘輸入,再通過鎖相環( PLL),電路模塊產生內核時鐘(CCLK)和系統時鐘(SCLK),通過設置PLL相關寄存器實現對CCLK和SCLK的頻率控制‘拇1。時鐘頻率設置框圖如圖2.30所示。CGY

CCLK和SCLK均由VCO(壓控振蕩器)輸出的時鐘分頻后得到。VCO輸出時鐘頻率由PI_,L控制寄存器(PLL_CTL)設置,CCLK和SCLK對VCO的分頻因子由PLL分頻寄存器( PLL_DIV)設置。需要注意的是,VCO最小輸出時鐘頻率為50MHz,最大輸出頻率為內核時鐘CCLK頻率的最大值。對于ADSP- BF533,CCLK最大值為600MHz,而ADSP- BF532 /531的CCLK最大值為400MHz。所以VCO輸出頻率不應超出50MHz~CCLK。

用戶可以通過設置PLL分頻寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)確定CCLK,通過設置SSEL(PLL_DIV的0~3位)確定SCLK。

由于SCLK頻率不能高于CCLK的頻率,所以在對SSEL參數設置時,需要確定當前CCLK的頻率。假設外部時鐘輸入CLKIN=27MHz,將CCLK設置為594MHz (27×22),SCLK設置為11818MHz (594 /5)。

如表2. 18所示,在Blackfin處理器中,降低系統時鐘頻率可以有效降低系統功耗。例如,Blackfin處理器ADSP- BF533通過外部時鐘輸入引腳CLKIN接收外部時鐘源(10~40MHz)的時鐘輸入,再通過鎖相環( PLL),電路模塊產生內核時鐘(CCLK)和系統時鐘(SCLK),通過設置PLL相關寄存器實現對CCLK和SCLK的頻率控制‘拇1。時鐘頻率設置框圖如圖2.30所示。CGY

CCLK和SCLK均由VCO(壓控振蕩器)輸出的時鐘分頻后得到。VCO輸出時鐘頻率由PI_,L控制寄存器(PLL_CTL)設置,CCLK和SCLK對VCO的分頻因子由PLL分頻寄存器( PLL_DIV)設置。需要注意的是,VCO最小輸出時鐘頻率為50MHz,最大輸出頻率為內核時鐘CCLK頻率的最大值。對于ADSP- BF533,CCLK最大值為600MHz,而ADSP- BF532 /531的CCLK最大值為400MHz。所以VCO輸出頻率不應超出50MHz~CCLK。

用戶可以通過設置PLL分頻寄存器PLL_DIV中的CSEL(PLL_DIV的4~5位)確定CCLK,通過設置SSEL(PLL_DIV的0~3位)確定SCLK。

由于SCLK頻率不能高于CCLK的頻率,所以在對SSEL參數設置時,需要確定當前CCLK的頻率。假設外部時鐘輸入CLKIN=27MHz,將CCLK設置為594MHz (27×22),SCLK設置為11818MHz (594 /5)。

公網安備44030402000607

公網安備44030402000607