消除寄生效應的版圖設計技術

發布時間:2012/4/21 20:05:39 訪問次數:2185

影響CMOS電路可靠性的重要MT1430因素是閉鎖效應,即可控硅效應。目前消除閉鎖效應的方法有采用截止環、外延和埋層外延結構、介質隔離結構和偽收集極等。

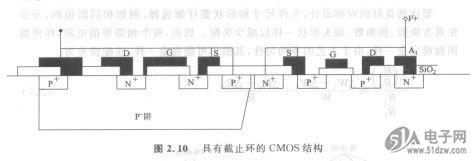

圖2. 10是具有截止環的CMOS結構。P阱的邊緣和每個N管的四周都用P+環包圍。P阱四周的P+環必須與地或負電源相連。N+環必然與襯底和正電源相連。因此,N+環是電路中的最高電位,P+環為最低電位,這樣硅片體內的電場主要集中在N+環與P+環之間。采用截止環結構,首先防止了場反型,同時使可控硅電阻大大減小,抑制了閉鎖效應。

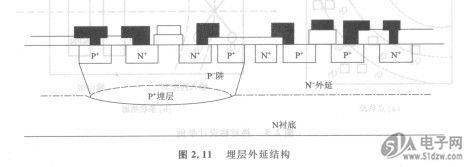

圖2. 11是埋層外延結構的示意圖。在N型襯底上外延N層,外延前在P阱下面位置擴P+埋層,P阱和P+埋層接通。這種埋層外延結構,比單純的外延結構抗閉鎖的效果更佳。一般用于低的開關導通電阻,大導通電流的模擬開關電路。

影響CMOS電路可靠性的重要MT1430因素是閉鎖效應,即可控硅效應。目前消除閉鎖效應的方法有采用截止環、外延和埋層外延結構、介質隔離結構和偽收集極等。

圖2. 10是具有截止環的CMOS結構。P阱的邊緣和每個N管的四周都用P+環包圍。P阱四周的P+環必須與地或負電源相連。N+環必然與襯底和正電源相連。因此,N+環是電路中的最高電位,P+環為最低電位,這樣硅片體內的電場主要集中在N+環與P+環之間。采用截止環結構,首先防止了場反型,同時使可控硅電阻大大減小,抑制了閉鎖效應。

圖2. 11是埋層外延結構的示意圖。在N型襯底上外延N層,外延前在P阱下面位置擴P+埋層,P阱和P+埋層接通。這種埋層外延結構,比單純的外延結構抗閉鎖的效果更佳。一般用于低的開關導通電阻,大導通電流的模擬開關電路。

公網安備44030402000607

公網安備44030402000607