并行進位同步二進制加法計數器

發布時間:2012/12/10 19:26:04 訪問次數:2526

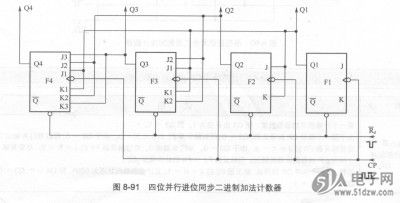

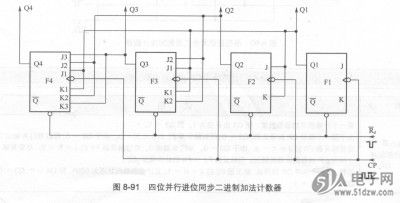

圖8-91所示是由4個JK觸發器構成的EP2S30F484C5四位并行進位同步二進制加法計數器,這一電路與前一個串行同步計數器電路相比有一點不同之處,就是電路中的JK觸發器有多個J和K輸入端,如觸發器F3有2個這樣的輸入端,觸發器F4則有3個J、K輸入端。

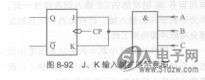

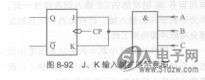

Jl、J2和J3是一個與門電路的3個輸入端,Kl、K2和K3是一個與門電路的3個輸入端。如果JK觸發器的J、K輸入端數目不夠用時,可使用附加的與門電路來擴展,如圖8-92所示。圖8-92 J、K輸入端擴展示意圖。

對于并行進位同步二進制加法計數器,計數前先清零,即在Rd端加上負脈沖,這樣計數器輸出狀態為0000,即Q4=O,Q3=0,Q2=0,Ql=O。下面根據輸入計數脈沖CP分成幾種情況分析這一電路的加法計數過程。

通過上述分析可知,計數脈沖CP是同時加到各JK觸發器的CP端,進位信號是通過本級的多個J、K輸入端實現的,各觸發器的進位信號是并行的,這種計數方式稱為并行同步計數。

圖8-91所示是由4個JK觸發器構成的EP2S30F484C5四位并行進位同步二進制加法計數器,這一電路與前一個串行同步計數器電路相比有一點不同之處,就是電路中的JK觸發器有多個J和K輸入端,如觸發器F3有2個這樣的輸入端,觸發器F4則有3個J、K輸入端。

Jl、J2和J3是一個與門電路的3個輸入端,Kl、K2和K3是一個與門電路的3個輸入端。如果JK觸發器的J、K輸入端數目不夠用時,可使用附加的與門電路來擴展,如圖8-92所示。圖8-92 J、K輸入端擴展示意圖。

對于并行進位同步二進制加法計數器,計數前先清零,即在Rd端加上負脈沖,這樣計數器輸出狀態為0000,即Q4=O,Q3=0,Q2=0,Ql=O。下面根據輸入計數脈沖CP分成幾種情況分析這一電路的加法計數過程。

通過上述分析可知,計數脈沖CP是同時加到各JK觸發器的CP端,進位信號是通過本級的多個J、K輸入端實現的,各觸發器的進位信號是并行的,這種計數方式稱為并行同步計數。

上一篇:串行進位同步二進制加法計數器

上一篇:同步二進制可逆計數器

公網安備44030402000607

公網安備44030402000607