非門的組成

發布時間:2014/2/2 11:37:15 訪問次數:881

如果將一個或門后面接上一個非門,便構成了或非門電路D78134GF如圖1-2所示。

它的輸出信號Z和輸入信號A、B之間是先“或”后“非”的關系,用數學函數式表達.

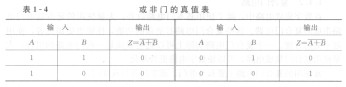

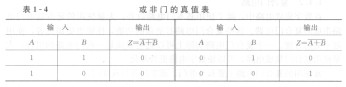

它表示Z是A、B之間是先“或”后“非”的結果。從或非門的邏輯功能可以很容易得到它的真值表,它的Z值實際上是或門Z輸出全部取反的結果,見表1-4。

如果把兩個與門輸出端分別接到一個或門的各個輸入端,然后在或門的輸

出端再接人一個非門,便構成了與或非門,如圖1-3所示。從圖中可以看出,

它是先“與”后“或”再“非”的邏輯關系。顯然其邏輯功能為:當輸入端任

何一組全為“1”時,輸出即為“0”;只有兩組輸入端中都至少有一個為“0”

時,輸出才能為“1”。用數學函數式表達.

它表示Z是在A、B和C,D分別相“與”之后,把這兩個相“與”的結果

再“或”一次,最后再取反的結果。根據與或非門的邏輯功能,

如果將一個或門后面接上一個非門,便構成了或非門電路D78134GF如圖1-2所示。

它的輸出信號Z和輸入信號A、B之間是先“或”后“非”的關系,用數學函數式表達.

它表示Z是A、B之間是先“或”后“非”的結果。從或非門的邏輯功能可以很容易得到它的真值表,它的Z值實際上是或門Z輸出全部取反的結果,見表1-4。

如果把兩個與門輸出端分別接到一個或門的各個輸入端,然后在或門的輸

出端再接人一個非門,便構成了與或非門,如圖1-3所示。從圖中可以看出,

它是先“與”后“或”再“非”的邏輯關系。顯然其邏輯功能為:當輸入端任

何一組全為“1”時,輸出即為“0”;只有兩組輸入端中都至少有一個為“0”

時,輸出才能為“1”。用數學函數式表達.

它表示Z是在A、B和C,D分別相“與”之后,把這兩個相“與”的結果

再“或”一次,最后再取反的結果。根據與或非門的邏輯功能,

公網安備44030402000607

公網安備44030402000607