可預置數4位二一十進制加/減計數器CD40192/CD40193

發布時間:2015/1/29 19:47:00 訪問次數:6073

可預置數4位二一十進制加/減計數器CD40192/CD40193。

電路名稱: HA2-2505-5可預置數4位二一十進制加/減計數器集成電路。

電路特點:該電路采用雙時鐘計數輸入方式,加、減計數分別采用各自的時鐘通道,計數方向(加或減)由時鐘進入的通道決定。電路計數采用二一十進制編碼,具有進位輸出Qco和借位輸出QBO引腳。

該電路為16引腳如圖3 - 20 (h)所示,其中,CPu為加計數時鐘脈沖輸入端;CPD為減計數時鐘脈沖輸入端;4個預置數端D1~D4;4個計數輸出端oi~04; -個預置數控制端PE,加高電平時預置數;一個復位端R,加高電平時計數器清O;還有一個進位端Qcc)和一個借位端QB()。

CD40192在作加計數使用時,要將CPD接高電平,計數脈沖由CPu端輸入,在脈沖上升沿的作用下,計數器作加計數。當用作減計數時,需將CPu接高電平,計數脈沖由CPD端輸入,在脈沖上升沿的作用下,計數器作減計數。

CD40192的預置數是加在預置數端D1~D4上的高、低電平,高電平代表1,低電平代表0,當預置數后,只要在PE端和R端加上低電平后,預置數便會被傳送到Ql~Q4端;當需要作加、減計數時,只要在CPu或CPD端加上正脈沖后,oi~Q4端就會作加或減的

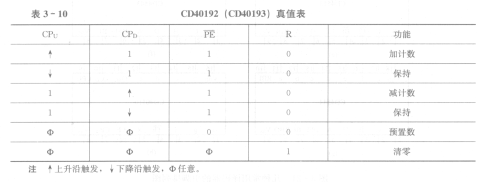

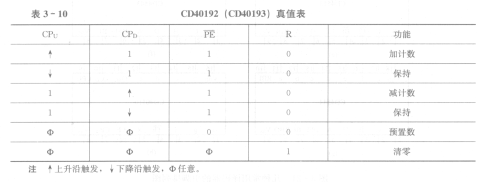

計數輸出;當需要清0時,只需在R端加上高電平,這時oi~04變為低電平O;當加計數到1001(十進制數10)時,Qco向高位計數單元輸出進位的負脈沖;當減計數到0000(十進制數O)時,QBO向高位計數單元輸出借位負脈沖。CD40192 (CD40193)寞值表見

表3 - 10。

可預置數4位二一十進制加/減計數器CD40192/CD40193。

電路名稱: HA2-2505-5可預置數4位二一十進制加/減計數器集成電路。

電路特點:該電路采用雙時鐘計數輸入方式,加、減計數分別采用各自的時鐘通道,計數方向(加或減)由時鐘進入的通道決定。電路計數采用二一十進制編碼,具有進位輸出Qco和借位輸出QBO引腳。

該電路為16引腳如圖3 - 20 (h)所示,其中,CPu為加計數時鐘脈沖輸入端;CPD為減計數時鐘脈沖輸入端;4個預置數端D1~D4;4個計數輸出端oi~04; -個預置數控制端PE,加高電平時預置數;一個復位端R,加高電平時計數器清O;還有一個進位端Qcc)和一個借位端QB()。

CD40192在作加計數使用時,要將CPD接高電平,計數脈沖由CPu端輸入,在脈沖上升沿的作用下,計數器作加計數。當用作減計數時,需將CPu接高電平,計數脈沖由CPD端輸入,在脈沖上升沿的作用下,計數器作減計數。

CD40192的預置數是加在預置數端D1~D4上的高、低電平,高電平代表1,低電平代表0,當預置數后,只要在PE端和R端加上低電平后,預置數便會被傳送到Ql~Q4端;當需要作加、減計數時,只要在CPu或CPD端加上正脈沖后,oi~Q4端就會作加或減的

計數輸出;當需要清0時,只需在R端加上高電平,這時oi~04變為低電平O;當加計數到1001(十進制數10)時,Qco向高位計數單元輸出進位的負脈沖;當減計數到0000(十進制數O)時,QBO向高位計數單元輸出借位負脈沖。CD40192 (CD40193)寞值表見

表3 - 10。

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607