RASM-712PX CMOS門電路扇出數的計算分兩種情況

發布時間:2020/2/9 12:17:53 訪問次數:9978

rasm-712pxrol(驅動門),jvol=頁面下(3.1.5)

圖3.1.4 扇出數的計算,(a)拉電流負載 (b)灌電流負載

一般邏輯器件的數據手冊中,并不給出扇出數,而必須用計算或用實驗的方法求得,并注意在設計時留有余地,以保證數字電路或系統能正常地運行。在實際的工程設計中,如果輸出高電平電流foh與輸出低電平電流fol不相等,則Ⅳol≠Ⅳoh,常取二者中的最小值。

對于cmos門電路扇出數的計算分兩種情況,一種是帶cmos負載,另一種是帶ttl負載。負載類型不同,數據手冊中給出的輸出高電平電流jlh或者輸出低電平電流fll也不相同。當所帶負載為cmos電路時,根據數據手冊(或附錄a),查得74hc/74hct的輸出電流roⅡ=~2oua,jol=20 uao輸入電流jⅢ=1ua,ril=~1ua。數據前的負號表示電流從器件流出,反之表示電流流人器件,計算時只取絕對值。所以Ⅳoh=Ⅳol=20 ua/1 ua=20,即最多可接同類電路的輸人端數為20個。

上述cmos扇出數的計算是保證cmos驅動門的高電平輸出為4.9Ⅴ。如果允許其高電平輸出降至ttl門的邏輯電平3,84v(低電平亦然),則joh和jol分別為-4ma和4ma,此時計算出的扇出數為4000,實際不可能達到這么大的數,因為cmos門的輸入電容比較大,電容的充放電電流不能忽略。74hct系列與ttl兼容,如果cmos所帶負載為74ls系列的ttl門電

路,此時roh=fol=4 ma,而rm=0.02ma,jil=0.4 ma,根據式(3.1.4)可計算高電平輸出時的扇出數Ⅳoh=ic=5/1-1u=j=200

根據式(3.1.5)可計算低電平輸出時的扇出數Ⅳol=u≠uo=10邏輯電路性曲線的可變電阻區可以看到,當vgs一定時,d、s之間可近似等效為線性電阻。vgs越大,輸出特性曲線越傾斜,等效電阻越小。此時mos管可以看成一個受vcs控制的可變電阻。 cs的取值足夠大時,使得rd遠遠大于d、s之間的等效電阻時,電路輸出為低電平。

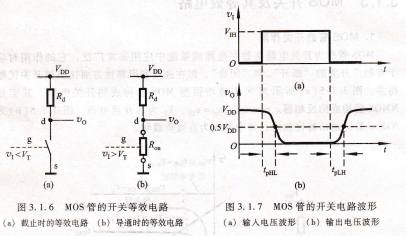

由此可見,mos管相當于一個由vgs控制的無觸點開關,當輸人為低電平時,mos管截止,相當于開關“斷開”,輸出為高電平,其等效電路如圖3.1.6(a)所示;當輸入為高電平時,mos管工作在可變電阻區,相當于開關“閉合”,輸出為低電平,其等效電路如圖3.1.6(b)所示。圖中r。n為mos管導通時的等效電阻,約在1 kΩ以內。

圖3.1.6 mos管的開關等效電路,(a)截止時的等效電路 (b)導通時的等效電路

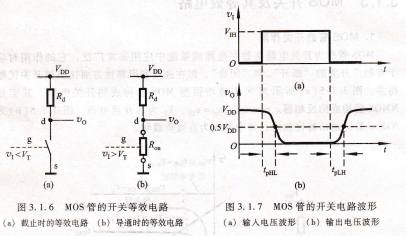

圖3.1.7 mos管的開關電路波形,(a)輸人電壓波形 (b〉輸出電壓波形

mos管的開關特性,在圖3.1.5(a)所示mos管的開關電路的輸人端,加一個理想的脈沖波形,如圖3.1.7所示。由于mos管中柵極與襯底間電容cgb(即數據手冊中的輸入電容ci)、漏極與襯底間電容cdb、柵極與漏極電容cgd以及導通電阻等的存在,使其在導通和閉合兩種狀態之間轉換時,不可避免地受到電容充、放電過程的影響。輸出電壓vo的波形已不是和輸人一樣的理想脈沖,上升和下降沿都變得緩慢了,而且輸出電壓的變化滯后于輸入電壓的變化。

cmos反相器,由n溝道和p溝道兩種mosfet組成的電路稱為互補mos或cmos電路,這在本書模擬部分已做了較詳細的討論,這里著重討論它作為數字電路的.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

rasm-712rol(驅動門),jvol=頁面下(3.1.5)

圖3.1.4 扇出數的計算,(a)拉電流負載 (b)灌電流負載

一般邏輯器件的數據手冊中,并不給出扇出數,而必須用計算或用實驗的方法求得,并注意在設計時留有余地,以保證數字電路或系統能正常地運行。在實際的工程設計中,如果輸出高電平電流foh與輸出低電平電流fol不相等,則Ⅳol≠Ⅳoh,常取二者中的最小值。

對于cmos門電路扇出數的計算分兩種情況,一種是帶cmos負載,另一種是帶ttl負載。負載類型不同,數據手冊中給出的輸出高電平電流jlh或者輸出低電平電流fll也不相同。當所帶負載為cmos電路時,根據數據手冊(或附錄a),查得74hc/74hct的輸出電流roⅡ=~2oua,jol=20 uao輸入電流jⅢ=1ua,ril=~1ua。數據前的負號表示電流從器件流出,反之表示電流流人器件,計算時只取絕對值。所以Ⅳoh=Ⅳol=20 ua/1 ua=20,即最多可接同類電路的輸人端數為20個。

上述cmos扇出數的計算是保證cmos驅動門的高電平輸出為4.9Ⅴ。如果允許其高電平輸出降至ttl門的邏輯電平3,84v(低電平亦然),則joh和jol分別為-4ma和4ma,此時計算出的扇出數為4000,實際不可能達到這么大的數,因為cmos門的輸入電容比較大,電容的充放電電流不能忽略。74hct系列與ttl兼容,如果cmos所帶負載為74ls系列的ttl門電

路,此時roh=fol=4 ma,而rm=0.02ma,jil=0.4 ma,根據式(3.1.4)可計算高電平輸出時的扇出數Ⅳoh=ic=5/1-1u=j=200

根據式(3.1.5)可計算低電平輸出時的扇出數Ⅳol=u≠uo=10邏輯電路性曲線的可變電阻區可以看到,當vgs一定時,d、s之間可近似等效為線性電阻。vgs越大,輸出特性曲線越傾斜,等效電阻越小。此時mos管可以看成一個受vcs控制的可變電阻。 cs的取值足夠大時,使得rd遠遠大于d、s之間的等效電阻時,電路輸出為低電平。

由此可見,mos管相當于一個由vgs控制的無觸點開關,當輸人為低電平時,mos管截止,相當于開關“斷開”,輸出為高電平,其等效電路如圖3.1.6(a)所示;當輸入為高電平時,mos管工作在可變電阻區,相當于開關“閉合”,輸出為低電平,其等效電路如圖3.1.6(b)所示。圖中r。n為mos管導通時的等效電阻,約在1 kΩ以內。

圖3.1.6 mos管的開關等效電路,(a)截止時的等效電路 (b)導通時的等效電路

圖3.1.7 mos管的開關電路波形,(a)輸人電壓波形 (b〉輸出電壓波形

mos管的開關特性,在圖3.1.5(a)所示mos管的開關電路的輸人端,加一個理想的脈沖波形,如圖3.1.7所示。由于mos管中柵極與襯底間電容cgb(即數據手冊中的輸入電容ci)、漏極與襯底間電容cdb、柵極與漏極電容cgd以及導通電阻等的存在,使其在導通和閉合兩種狀態之間轉換時,不可避免地受到電容充、放電過程的影響。輸出電壓vo的波形已不是和輸人一樣的理想脈沖,上升和下降沿都變得緩慢了,而且輸出電壓的變化滯后于輸入電壓的變化。

cmos反相器,由n溝道和p溝道兩種mosfet組成的電路稱為互補mos或cmos電路,這在本書模擬部分已做了較詳細的討論,這里著重討論它作為數字電路的.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

熱門點擊

熱門點擊

- LM92CIMX/NOPB 并行相加串行進位的方式

- DTSM-63K-V 判斷LED數碼管的好壞

- TPS61230DRCR 變速恒頻電源系統的結構與配置

- 65474-001上升沿觸發和下降沿觸發的D觸發器邏輯符號

- RASM-712PX CMOS門電路扇出數的計算分兩種情況

- LQP03TN15NJ02D 脈沖的寬度的電源頻率

- PE-1008CX150K 電流互感器檢測電瓶充電器內部電流的大小

- NSCW455AT 產生低電壓的原因及保護指標

- BC856CMTF 空穴的遷移率比電子低

- SN74LS247 邏輯功能的仿真與測試

推薦電子資訊

推薦電子資訊

- iPhone5S/iPhone5C獲工信部認證

- 庫克一直看好中國市場的巨大潛力,并且自去年3月以來他已... [詳細]

公網安備44030402000607

公網安備44030402000607