І»Н¬лҠИЭЦөөДЖҘЕдФOУӢ

°lІј•rйg:2016/6/28 23:29:22 ФLҶ–ҙО”ө:519

ҲD8.19(a)ЛщКҫөД2Ц»ҫ§уw№ЬөД°жҲD·ҪПтІ»Н¬,ЖҘЕдРФДЬәЬІо;ҲD8.19(b)ЛщКҫөД2Ц»ҫ§уw№ЬөД°жҲD·ҪПтТ»ЦВ,ө«КЗғЙҫ§уw№ЬФҙВ©ҳOөДЦЬҮъӯhҫіІ»Н¬,ADS1118Я@•юТэЖрФҙВ©ҳOөД“Ҫлsқв¶ИЎў¶аҫ§№иҝМОgЛЩВКөДІ»ЖҘЕд,ТтҙЛ•юФцјУғЙҫ§уw№ЬЦ®йgөДІ»ЖҘЕд;ҲD8.19(c)НЁЯ^ФцјУЎ°ИЯУаЎұҶОФӘұЈЧCБЛГҝӮҖҫ§уw№ЬЦЬҮъөДӯhҫіПаН¬,ТтҙЛңpРЎБЛҫ§уw№ЬөДІ»ЖҘЕдЎЈ

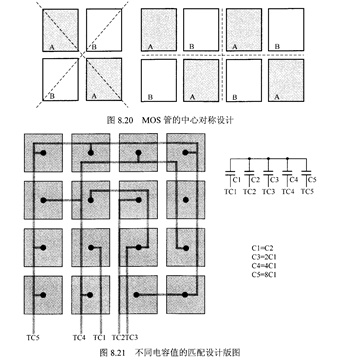

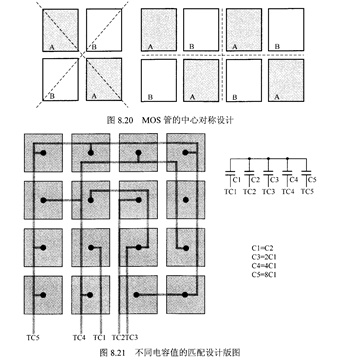

ҲD8.ўДЛщКҫКЗІЙУГЦШРДЦШәПөДMOS№ЬФOУӢЎЈҲD8.21ҪoіцБЛ5ӮҖлҠИЭЦөЦ®ұИһй1ЎГўұўІўҙ8өДЖҘЕдлҠИЭФЪІЙУГБЛҶОФӘФӘЖчјюҸНЦЖјјРgЎў№«УГЦШРДФOУӢјјРgәуөД°жҲD,ҫCәПІЙУГЯ@Р©јјРg,ҝЙТФМбёЯ¶аӮҖлҠИЭЦ®йgөДЖҘЕдРФДЬЎЈ

ІЙУГ°жҲDЖҘЕдФOУӢјјРgәуҝЙТФМбёЯФӘЖчјюөДЖҘЕдРФДЬ,ө«КЗ•юФцјУРҫЖ¬Гж·e,ІјҫҖТІ•юұИЭ^А§лy,ЯBҫҖөДјДЙъР§‘Ә•юПЮЦЖЖҘЕдҫ«¶ИЎЈ

ҲD8.19(a)ЛщКҫөД2Ц»ҫ§уw№ЬөД°жҲD·ҪПтІ»Н¬,ЖҘЕдРФДЬәЬІо;ҲD8.19(b)ЛщКҫөД2Ц»ҫ§уw№ЬөД°жҲD·ҪПтТ»ЦВ,ө«КЗғЙҫ§уw№ЬФҙВ©ҳOөДЦЬҮъӯhҫіІ»Н¬,ADS1118Я@•юТэЖрФҙВ©ҳOөД“Ҫлsқв¶ИЎў¶аҫ§№иҝМОgЛЩВКөДІ»ЖҘЕд,ТтҙЛ•юФцјУғЙҫ§уw№ЬЦ®йgөДІ»ЖҘЕд;ҲD8.19(c)НЁЯ^ФцјУЎ°ИЯУаЎұҶОФӘұЈЧCБЛГҝӮҖҫ§уw№ЬЦЬҮъөДӯhҫіПаН¬,ТтҙЛңpРЎБЛҫ§уw№ЬөДІ»ЖҘЕдЎЈ

ҲD8.ўДЛщКҫКЗІЙУГЦШРДЦШәПөДMOS№ЬФOУӢЎЈҲD8.21ҪoіцБЛ5ӮҖлҠИЭЦөЦ®ұИһй1ЎГўұўІўҙ8өДЖҘЕдлҠИЭФЪІЙУГБЛҶОФӘФӘЖчјюҸНЦЖјјРgЎў№«УГЦШРДФOУӢјјРgәуөД°жҲD,ҫCәПІЙУГЯ@Р©јјРg,ҝЙТФМбёЯ¶аӮҖлҠИЭЦ®йgөДЖҘЕдРФДЬЎЈ

ІЙУГ°жҲDЖҘЕдФOУӢјјРgәуҝЙТФМбёЯФӘЖчјюөДЖҘЕдРФДЬ,ө«КЗ•юФцјУРҫЖ¬Гж·e,ІјҫҖТІ•юұИЭ^А§лy,ЯBҫҖөДјДЙъР§‘Ә•юПЮЦЖЖҘЕдҫ«¶ИЎЈ

ЙПТ»ЖӘЈәЖҘЕдMOsҫ§уw№Ь

ЙПТ»ЖӘЈәЖҘЕдөДФӯ„t

ҹбйTьc“ф

ҹбйTьc“ф

- TDDBР§‘ӘөД“фҙ©ҷCЦЖ

- Эp“ҪлsФҙВ©(LDD)

- өИұИАэҝsРЎөД3ӮҖТҺ„t

- ҪзГж‘BөД®aЙъЯ^іМ

- өН„ЭүҫёЯ¶ИөДҡWД·ҪУУ|

- MOs№ЬөДҢҚлH°жҲD

- MOsFETөДй“ЦөлҠүә

- ҝ№·ҙЙдҢУ

- Хы°елҠеғәНҲDРОлҠеғ

- жҮ№и»ҜОп(NiSi)

НЖЛ]јјРgЩYБП

НЖЛ]јјРgЩYБП

- УІұPКҪMP3ІҘ·ЕЖчҪKјүёД

- Т»ҙОЕјИ»өДҷC•юОТҪYЧRБЛNE0 2511,ДЗКЗТ»ӮҖЯh·ҪөД... [Ф”јҡ]

- 12О»ДЈ”өЮD“QЖч (ADC)…ў

- ИэҪЗәҜ”өјУЛЩЖч (TMU)ПөБР

- ҶОРҫЖ¬Ў°Е“РРІҙЎұТ»уw»Ҝ·Ҫ°ёМҪҫҝ

- CoolSiCРӨМШ»щ¶юҳO№ЬјјРg

- ј{ОўGaN SafeПөБРNV6515ЈЁ650

- ЕRҪзҢ§НЁДЈКҪЈЁCrMЈ©Ф”Зй

- ¶аГҪуw…fМҺАнЖчSM501ФЪЗ¶ИлКҪПөҪyЦРөД‘ӘУГ

- »щУЪIEEE802.11bөДEPAңШ¶ИЧғЛНЖч

- QUICCEngineРВТэЗжНЖ„УIPҫWҪjёпРВ

- SoCГжКА°ЛДкәуөД®aҳIҷCУц

- MPC8xxПөБРМҺАнЖчөДЗ¶ИлКҪПөҪyлҠФҙФOУӢ

- dsPICј°ЖдФЪҪ»БчЧғоlХ{ЛЩЦРөД‘ӘУГСРҫҝ

№«ҫW°ІӮд44030402000607

№«ҫW°ІӮд44030402000607