芯片電流引腳上磁珠與去耦電容的位置

發布時間:2017/6/22 21:12:32 訪問次數:1079

芯片電流引腳上磁珠與去耦電容的位置

【現象描述】

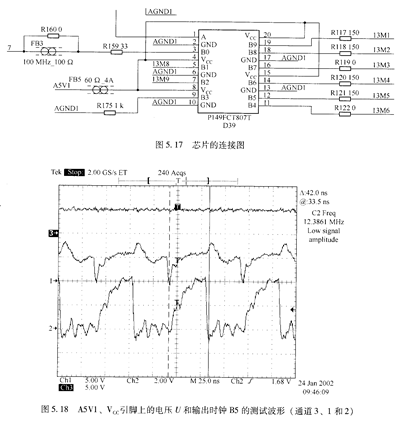

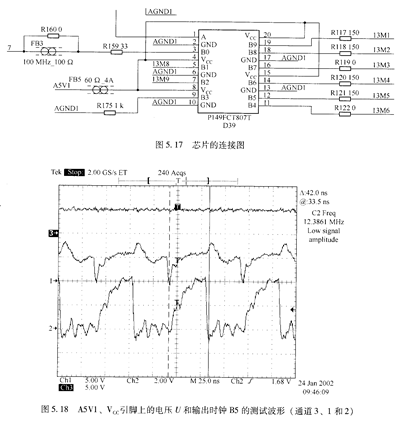

某產品PCB中有一時鐘驅動芯片,在供電M25P32-VMP6TG電源A5Ⅴ1靠近時鐘驅動芯片電源處并聯了10uF的濾波電容C】”和0,1uF的去耦電容C202(圖5.17沒有畫出),并經過磁珠FB5(17010145鐵氧體-EMI磁珠-60Ω±25%-4.0A-⒛6)后,送到芯片的Ⅴ∝電源引腳處,如圖5.17所示。結果發現輸出的時鐘波形信號質量極差,并且占空比也發生了變化,進一步測試發現芯片Ⅴcc引腳上的電壓有嚴重的振蕩和跌落現象,振蕩的頻率和輸出時鐘的頻率相同,在Ⅴ∝引腳上的電壓跌落時,輸出時鐘的上升沿變得很緩,測試波形如圖5,18所示。

芯片電流引腳上磁珠與去耦電容的位置

【現象描述】

某產品PCB中有一時鐘驅動芯片,在供電M25P32-VMP6TG電源A5Ⅴ1靠近時鐘驅動芯片電源處并聯了10uF的濾波電容C】”和0,1uF的去耦電容C202(圖5.17沒有畫出),并經過磁珠FB5(17010145鐵氧體-EMI磁珠-60Ω±25%-4.0A-⒛6)后,送到芯片的Ⅴ∝電源引腳處,如圖5.17所示。結果發現輸出的時鐘波形信號質量極差,并且占空比也發生了變化,進一步測試發現芯片Ⅴcc引腳上的電壓有嚴重的振蕩和跌落現象,振蕩的頻率和輸出時鐘的頻率相同,在Ⅴ∝引腳上的電壓跌落時,輸出時鐘的上升沿變得很緩,測試波形如圖5,18所示。

熱門點擊

熱門點擊

- 以典型的雙阱CMOS反相器為例介紹CMOS工

- CVD工藝原理

- 電感加熱器

- 屏蔽電纜的屏蔽層一定要360°搭接處理。

- CMOS電路的輸出端不能直接連到一起

- 導線的電阻會隨著頻率的升高而增加

- ESD干擾原理可以從兩方面來考慮

- 硅的濕法刻蝕

- 芯片電流引腳上磁珠與去耦電容的位置

- 對于開關電源的差模傳導騷擾

推薦技術資料

推薦技術資料

- 硬盤式MP3播放器終級改

- 一次偶然的機會我結識了NE0 2511,那是一個遠方的... [詳細]

公網安備44030402000607

公網安備44030402000607