某PCB沒有分地時的數字電路噪聲干擾

發布時間:2017/6/28 19:15:25 訪問次數:422

可見,分地設計不能輕易實施,實際產品設計中,在以下幾種情況下,才可以考慮分地,TAS5760MDAPR總體上可以分為兩種:

(1)通常發生在單面板和雙面板情況下。當單面板和雙面板注定不能設計出較完整的地平面時,可以通過分地適當降低產品整體的EMC性能,以改善數模混合電路之間的干擾問題。

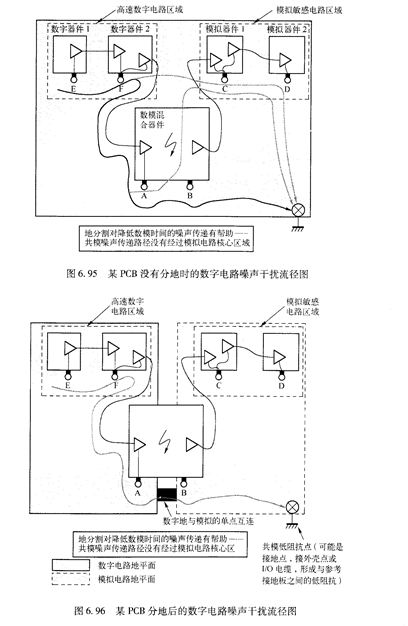

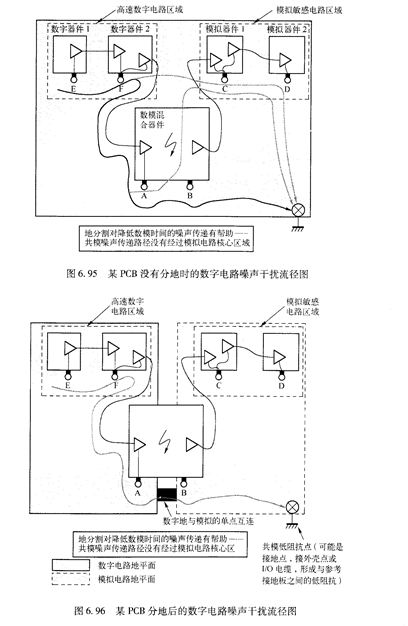

(2)發生在本來可以具有地平面的4層板以上的PCB設計中。如圖6.95和圖6.96所示分別是某一PCB沒有分地時的數字電路噪聲干擾流徑圖和某一PCB分地時的數字電路噪聲干擾流徑圖。

可見,分地設計不能輕易實施,實際產品設計中,在以下幾種情況下,才可以考慮分地,TAS5760MDAPR總體上可以分為兩種:

(1)通常發生在單面板和雙面板情況下。當單面板和雙面板注定不能設計出較完整的地平面時,可以通過分地適當降低產品整體的EMC性能,以改善數模混合電路之間的干擾問題。

(2)發生在本來可以具有地平面的4層板以上的PCB設計中。如圖6.95和圖6.96所示分別是某一PCB沒有分地時的數字電路噪聲干擾流徑圖和某一PCB分地時的數字電路噪聲干擾流徑圖。

熱門點擊

熱門點擊

- 二氧化硅的濕法刻蝕

- 鎢的刻蝕

- 氮化硅的干法刻蝕

- 埋層的制備

- 芯片互連技術

- 兩平行導線之間的距離對其寄生電容的影響

- 目前市場上出現的BGA封裝,按基板的種類

- WLR――硅片級可靠性測試

- 電子束光刻膠

- 光刻工藝對掩模板的質量要求歸納

推薦技術資料

推薦技術資料

- 業余條件下PCM2702

- PGM2702采用SSOP28封裝,引腳小而密,EP3... [詳細]

公網安備44030402000607

公網安備44030402000607