IDT74FST3364Q 邏輯功能的仿真與測試

發布時間:2019/10/10 13:28:10 訪問次數:1940

IDT74FST3364Q例2.3.1是圖2,3,2所示電路的結構描述方式。第1行以雙斜線(//)開始a到本行結尾之間的文本是一個注釋,對se1這個電路進行簡單的說明。第2行以關

鍵詞module開始聲明了一個模塊,module后面跟有模塊名(mux2to1)和端bU3

口名(a、b、se1、。ut)列表。端口名列表給出了該模塊的輸人端口、輸出端口,端 圖2.3.2簡單的門電路口用圓括號括起來,多個端口之間以逗號進行分隔。每一條語句以分號結尾。接著,以關鍵詞input和output定義了該模塊的輸人端口、輸出端口。端口的數據類型默認為wire類型,此處將電路內部的結點信號(selnot、a1、b1)定義為wire類型。電路的結構(即邏輯功能)由Ⅴerilog內部預定義的基本門級元件(not、and、or)進行描述,每個門級元件后面包含一個調用名(U1、U2等)和由圓括號括起來、以逗號分隔的輸出端口以及輸入端口,Verilog規定輸出端口總是位于左邊的第1個位置,輸人端口跟在后面。例如,調用名為U4的或門輸出端口是out、輸入端口是a1和b1。調用名可以直接使用,不需要事先定義,并且調用基本門級元件時,調用名可以省略。最后模塊以endmodule結尾(注意后面沒有分號)。由于這個模塊描‘述了電路的邏輯功能,故將該模塊稱為設計塊。

對一個實際的門電路來說,信號從輸入端口傳到輸出端口存在著延時,在使用HDL進行邏輯功能仿真時,說明門電路的延時有時是必要的。有關這方面的內容可參考文獻[11],本書作為Verilog方面的人門書籍,沒有介紹這方面的內容。

邏輯功能的仿真與測試

一旦邏輯電路的設計塊完成后,接下來就要測試這個設計塊描述的邏輯功能是否正確。為此必須在輸人端口加入測試信號,以便從輸出端口檢測其結果是否正確,這一過程常稱為搭建測試平臺①。根據仿真軟件的不同,搭建測試平臺的方法也不同,本書使用Quartus Ⅱ軟件(該軟件使用方法見附錄B)②進行仿真,用該軟件以波形圖的方式建立一個矢量波形文件(擴展名為.vwf)作為激勵信號。

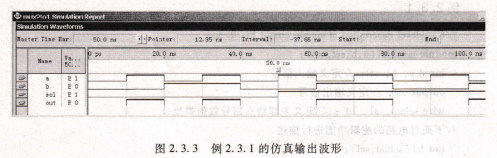

對例2.3.1進行仿真時,首先進人Quartus Ⅱ軟件,創建一個新的工程設計項目,并使用文本編輯器輸入源程序,再對該設計項目進行編譯,然后使用波形編輯器創建一個新的矢量波形文件,最后進行邏輯功能仿真,得到圖2,3.3所示的波形。由圖可知,在0~50 ns期間,由于se1=o,所以輸出out與輸人a相同;50~100 ns期間,由于se1=1,故輸出out與輸人b相同。分析表明該設計塊描述的邏輯功能是正確的。

① 系英文Test Bench的譯稱。

② Altera公司自行研制的軟件.為該公司生產的可編程邏輯器件提供了一ˉ個綜合開發環境。

IDT74FST3364Q例2.3.1是圖2,3,2所示電路的結構描述方式。第1行以雙斜線(//)開始a到本行結尾之間的文本是一個注釋,對se1這個電路進行簡單的說明。第2行以關

鍵詞module開始聲明了一個模塊,module后面跟有模塊名(mux2to1)和端bU3

口名(a、b、se1、。ut)列表。端口名列表給出了該模塊的輸人端口、輸出端口,端 圖2.3.2簡單的門電路口用圓括號括起來,多個端口之間以逗號進行分隔。每一條語句以分號結尾。接著,以關鍵詞input和output定義了該模塊的輸人端口、輸出端口。端口的數據類型默認為wire類型,此處將電路內部的結點信號(selnot、a1、b1)定義為wire類型。電路的結構(即邏輯功能)由Ⅴerilog內部預定義的基本門級元件(not、and、or)進行描述,每個門級元件后面包含一個調用名(U1、U2等)和由圓括號括起來、以逗號分隔的輸出端口以及輸入端口,Verilog規定輸出端口總是位于左邊的第1個位置,輸人端口跟在后面。例如,調用名為U4的或門輸出端口是out、輸入端口是a1和b1。調用名可以直接使用,不需要事先定義,并且調用基本門級元件時,調用名可以省略。最后模塊以endmodule結尾(注意后面沒有分號)。由于這個模塊描‘述了電路的邏輯功能,故將該模塊稱為設計塊。

對一個實際的門電路來說,信號從輸入端口傳到輸出端口存在著延時,在使用HDL進行邏輯功能仿真時,說明門電路的延時有時是必要的。有關這方面的內容可參考文獻[11],本書作為Verilog方面的人門書籍,沒有介紹這方面的內容。

邏輯功能的仿真與測試

一旦邏輯電路的設計塊完成后,接下來就要測試這個設計塊描述的邏輯功能是否正確。為此必須在輸人端口加入測試信號,以便從輸出端口檢測其結果是否正確,這一過程常稱為搭建測試平臺①。根據仿真軟件的不同,搭建測試平臺的方法也不同,本書使用Quartus Ⅱ軟件(該軟件使用方法見附錄B)②進行仿真,用該軟件以波形圖的方式建立一個矢量波形文件(擴展名為.vwf)作為激勵信號。

對例2.3.1進行仿真時,首先進人Quartus Ⅱ軟件,創建一個新的工程設計項目,并使用文本編輯器輸入源程序,再對該設計項目進行編譯,然后使用波形編輯器創建一個新的矢量波形文件,最后進行邏輯功能仿真,得到圖2,3.3所示的波形。由圖可知,在0~50 ns期間,由于se1=o,所以輸出out與輸人a相同;50~100 ns期間,由于se1=1,故輸出out與輸人b相同。分析表明該設計塊描述的邏輯功能是正確的。

① 系英文Test Bench的譯稱。

② Altera公司自行研制的軟件.為該公司生產的可編程邏輯器件提供了一ˉ個綜合開發環境。

熱門點擊

熱門點擊

- BS250優先編碼器74HC147

- 施密特觸發器用在去抖電路中的工作原理

- 程序存儲器和數據存儲器具有各自的總線

- 環網柜DTU與開閉所DTU的比較

- 單環網接線

- 光纖通信的優點

- 行列碼校驗又稱為方陣碼校驗或者水平垂直奇偶校

- 重合器(Recbser)是用于配電網自動化的

- 74435586800 四變量卡諾圖

- 通信規約的概念

推薦技術資料

推薦技術資料

- 業余條件下PCM2702

- PGM2702采用SSOP28封裝,引腳小而密,EP3... [詳細]

公網安備44030402000607

公網安備44030402000607