SN74AUC245RGYR EN為芯片的使能信號

發布時間:2019/10/14 13:23:50 訪問次數:1673

SN74AUC245RGYRten1p

-1 bitAdder t12(A[2],B[2],tcmp[2],Suln[2],temp[3]);

-1 bltAdder u3(A[3],B[3],temp[3],Sum[3],temp[4]);

Cout=temp[4];

cnd

endrnoduic

module l bitAdder(A,B,Ci,Sum,Co);

input A,B,Ci;

output sum,Co;

assign sum=A^B^Ci;

endmodule

圖4.4.4(a)所示是帶有使能控制端的8線-3線優先編碼該電路的行為級描述。

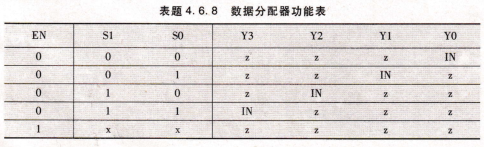

1路-4路數據分配器電路的功能表如表題4.6.8所示,IN為1路數據輸人信號,S1

S0為選擇信號,EN為芯片的使能信號,Y3~Y0為輸出信號。x為任意值,z為高阻態,要求:

用邏輯門設計該電路,寫出設計過程,畫出邏輯圖。

用verihlog HDL的行為建模方式描述該電路。

大多數數字系統中,除了需要具有邏輯運算和算術運算功能的組合邏輯電路外,還需要具有存儲功能的電路,組合電路與存儲電路相結合可構成時序邏輯電路,簡稱時序電路。本章將討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器①。著重討論它們的電路結構與工作原理,以及所實現的不同邏輯功能。此外,本章還將討論用verilog HDL描述鎖存器與觸發器的方法。

鎖存器和觸發器分別系latch和nip-flop的譯稱。

SN74AUC245RGYRten1p

-1 bitAdder t12(A[2],B[2],tcmp[2],Suln[2],temp[3]);

-1 bltAdder u3(A[3],B[3],temp[3],Sum[3],temp[4]);

Cout=temp[4];

cnd

endrnoduic

module l bitAdder(A,B,Ci,Sum,Co);

input A,B,Ci;

output sum,Co;

assign sum=A^B^Ci;

endmodule

圖4.4.4(a)所示是帶有使能控制端的8線-3線優先編碼該電路的行為級描述。

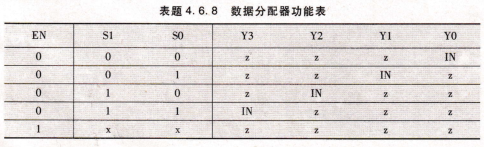

1路-4路數據分配器電路的功能表如表題4.6.8所示,IN為1路數據輸人信號,S1

S0為選擇信號,EN為芯片的使能信號,Y3~Y0為輸出信號。x為任意值,z為高阻態,要求:

用邏輯門設計該電路,寫出設計過程,畫出邏輯圖。

用verihlog HDL的行為建模方式描述該電路。

大多數數字系統中,除了需要具有邏輯運算和算術運算功能的組合邏輯電路外,還需要具有存儲功能的電路,組合電路與存儲電路相結合可構成時序邏輯電路,簡稱時序電路。本章將討論實現存儲功能的兩種邏輯單元電路,即鎖存器和觸發器①。著重討論它們的電路結構與工作原理,以及所實現的不同邏輯功能。此外,本章還將討論用verilog HDL描述鎖存器與觸發器的方法。

鎖存器和觸發器分別系latch和nip-flop的譯稱。

公網安備44030402000607

公網安備44030402000607