KM29N32000ATS 邏輯門控SR鎖存器

發布時間:2019/10/14 17:56:57 訪問次數:4515

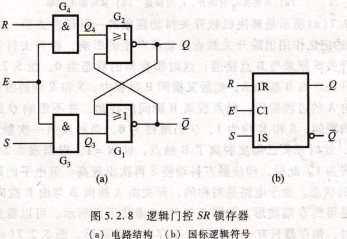

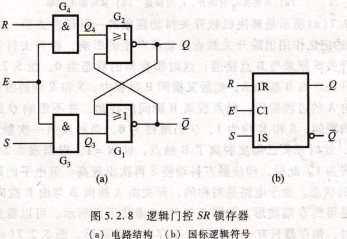

KM29N32000ATS前面所討論的基本sR鎖存器的輸出狀態是由輸入信號S或R直接控制的,而圖5.2.8(a)所示電路在基本SR鎖存器前增加了一對邏輯門G3、G4,用鎖存使能信號E控制鎖存器在某一指定時刻根據s、R輸入信號確定輸出狀態。這種鎖存器稱為邏輯門控SR鎖存器。與基本sR鎖存器相比,邏輯門控sR鎖存器增加了鎖存使能輸入端E。通過控制E端電平,可以實現多個鎖存器同步進行數據鎖存。

由圖5.2.8(a)可知,輸人信號s、R要經過門G3和G4傳遞,這兩個門同時受E信號控制。當E為0時,G3和G4被封鎖,s、R端的電平不會影響鎖存器的狀態;當E為1時,G3和G4打開,將S、R端的信號傳送到基本SR鎖存器的輸人端,從而確定0和0端的狀態。顯然,當E為1時,邏輯門控SR鎖存器的功能與表5.2.1一致。若這時輸人信號s=R=1,則Q=0=0,鎖存器處于不確定狀態。當E恢復為0時,由于O3、O4同時回到0,由Gl、G2構成的基本SR鎖存器出現圖5.2.3中⑤所指示的情況,將不能確定鎖存器的狀態,因此,這種鎖存器必須嚴格遵守sR=0的約束條件。

圖5.2.8(b)所示是邏輯門控SR鎖存器的邏輯符號,其方框內用C1和1R、1S表達內部邏輯之間的關聯關系。C表示這種關聯屬于控制類型,其后綴用標識序號“1”表示該輸人的邏輯狀態對所有以“1”作為前綴的輸人起控制作用。輸人R和S受C1的控制,故R和S之前分別以標識序號“1”作為前綴。圖5,2.8(b)所示的邏輯符號有兩個輸出端,分別以0和0命名。0端的小圓圈表示方框外部的邏輯狀態永遠是內部的邏輯非狀態,而0端狀態則永遠與內部狀態一致。這樣,不通過圖5.2.8(a)所示的邏輯電路,僅從抽象的邏輯符號也可以理解邏輯門控sR鎖存器各輸入、輸出信號之間的邏輯 E關系。

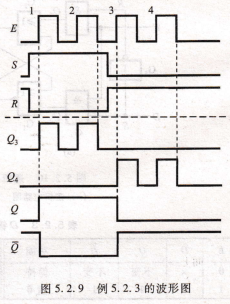

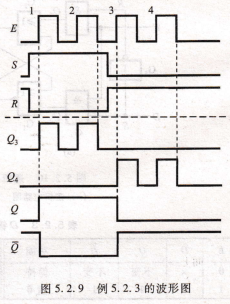

例5.2,3 圖5,2.8(a)所示邏輯門控SR鎖存器的E、S、R的波形如圖5.2,9中虛線上邊所示,鎖存器的原始狀態為Q=0,Q=1,試畫出Q3、Q4、0和0的波形。

解:從圖5.2.8(a)所示的邏輯電路圖得Q3=S・E,Q4=R・E。于是,可根據E、s和R的波形畫出o3和Q4的波形。圖5.2.8(a)中G1、G2構成基本SR鎖存器,再根據表5.2.1即可畫出0和O的波形,全部波形如圖5.2,9所示。

由于約束條件sR=0的限制,因而實際上很少直接應用這種邏輯門控SR鎖存器。但是,許多集成鎖存器和觸發器都是由這種鎖存器構成的,所以它仍是重要的基本邏輯單元電路。

KM29N32000ATS前面所討論的基本sR鎖存器的輸出狀態是由輸入信號S或R直接控制的,而圖5.2.8(a)所示電路在基本SR鎖存器前增加了一對邏輯門G3、G4,用鎖存使能信號E控制鎖存器在某一指定時刻根據s、R輸入信號確定輸出狀態。這種鎖存器稱為邏輯門控SR鎖存器。與基本sR鎖存器相比,邏輯門控sR鎖存器增加了鎖存使能輸入端E。通過控制E端電平,可以實現多個鎖存器同步進行數據鎖存。

由圖5.2.8(a)可知,輸人信號s、R要經過門G3和G4傳遞,這兩個門同時受E信號控制。當E為0時,G3和G4被封鎖,s、R端的電平不會影響鎖存器的狀態;當E為1時,G3和G4打開,將S、R端的信號傳送到基本SR鎖存器的輸人端,從而確定0和0端的狀態。顯然,當E為1時,邏輯門控SR鎖存器的功能與表5.2.1一致。若這時輸人信號s=R=1,則Q=0=0,鎖存器處于不確定狀態。當E恢復為0時,由于O3、O4同時回到0,由Gl、G2構成的基本SR鎖存器出現圖5.2.3中⑤所指示的情況,將不能確定鎖存器的狀態,因此,這種鎖存器必須嚴格遵守sR=0的約束條件。

圖5.2.8(b)所示是邏輯門控SR鎖存器的邏輯符號,其方框內用C1和1R、1S表達內部邏輯之間的關聯關系。C表示這種關聯屬于控制類型,其后綴用標識序號“1”表示該輸人的邏輯狀態對所有以“1”作為前綴的輸人起控制作用。輸人R和S受C1的控制,故R和S之前分別以標識序號“1”作為前綴。圖5,2.8(b)所示的邏輯符號有兩個輸出端,分別以0和0命名。0端的小圓圈表示方框外部的邏輯狀態永遠是內部的邏輯非狀態,而0端狀態則永遠與內部狀態一致。這樣,不通過圖5.2.8(a)所示的邏輯電路,僅從抽象的邏輯符號也可以理解邏輯門控sR鎖存器各輸入、輸出信號之間的邏輯 E關系。

例5.2,3 圖5,2.8(a)所示邏輯門控SR鎖存器的E、S、R的波形如圖5.2,9中虛線上邊所示,鎖存器的原始狀態為Q=0,Q=1,試畫出Q3、Q4、0和0的波形。

解:從圖5.2.8(a)所示的邏輯電路圖得Q3=S・E,Q4=R・E。于是,可根據E、s和R的波形畫出o3和Q4的波形。圖5.2.8(a)中G1、G2構成基本SR鎖存器,再根據表5.2.1即可畫出0和O的波形,全部波形如圖5.2,9所示。

由于約束條件sR=0的限制,因而實際上很少直接應用這種邏輯門控SR鎖存器。但是,許多集成鎖存器和觸發器都是由這種鎖存器構成的,所以它仍是重要的基本邏輯單元電路。

上一篇:IRF632 D鎖存器

公網安備44030402000607

公網安備44030402000607