MAX4788EXST觸發器時鐘信號

發布時間:2019/10/17 21:41:49 訪問次數:1316

MAX4788EXST下面以兩個實例來說明異步時序電路的分析過程。

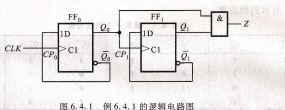

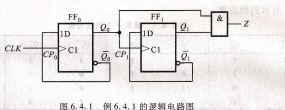

例6,4,1 分析圖6.4.1所示邏輯電路。

圖6,4.1 例6.4,1的邏輯電路圖

解:在圖6,4,1所示的電路中,兩觸發器FFO和FFI的CP0和CP1未共用時鐘信號,故屬于異步時序電路。

列出各邏輯方程組,這時需要考慮各觸發器時鐘信號CP″的作用:只有cpn=1發生后,觸發器才可能轉換狀態,當cp″=0,即幣.=1時,觸發器應保持原態。因此,觸發器的特性方程中應引人cpn而改寫為如下的狀態方程組

Q0n+1+1=q0qfh+qgkjh=q0n+qcp (6.4.1)

式(6.4.1)和式(6,4.2)中右邊的第二項表示,當觸發器沒有時鐘信號作用時,狀態保持不變。

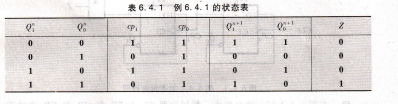

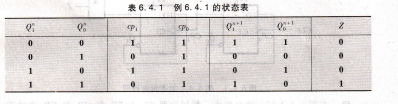

列出狀態表,列狀態表的方法與同步時序電路分析過程基本相似,只是還應注意各觸發器是否存在吼=1,因此,可在狀態表中增加cp()、cpl兩列。對應于輸人信號C乙K的每一個上升沿,cpO=1,將cp。和FFO的現態Q:代入式(6.4.1),從而得到Q:十1。因為只有對應于O0由0到1的跳變,才有印1=1,而對應于Qo由1到0的轉換9吼=0,所以在每一次0。的狀態轉換后,應首先根據FF1時鐘信號的邏輯表達式確定cp1,然后將FF1的現態Ol和相應的cp1代入式(6.4.2),求得其次態o:+1。如果從0IQ:為00開始推導,可以得到如表6.4,1所示的狀態表。

畫出狀態圖和時序圖

由表6.4.1所示的狀態表可畫出如圖6.4.2所示的狀態圖。

狀態不確定

圖6.4.2 例6.4.1的狀態圖 圖6.4.3 例6.4.1的時序圖

根據狀態圖和具體觸發器的傳輸延遲時間rpLH和莎pHL’可以畫出時序圖,如圖6.4.3所示。可以看出,由于兩個觸發器異步翻轉之間存在延遲,電路有短時間存在著不確定的狀態,如果使用74HCT74雙D觸發器實現圖6.4.1所示.

MAX4788EXST下面以兩個實例來說明異步時序電路的分析過程。

例6,4,1 分析圖6.4.1所示邏輯電路。

圖6,4.1 例6.4,1的邏輯電路圖

解:在圖6,4,1所示的電路中,兩觸發器FFO和FFI的CP0和CP1未共用時鐘信號,故屬于異步時序電路。

列出各邏輯方程組,這時需要考慮各觸發器時鐘信號CP″的作用:只有cpn=1發生后,觸發器才可能轉換狀態,當cp″=0,即幣.=1時,觸發器應保持原態。因此,觸發器的特性方程中應引人cpn而改寫為如下的狀態方程組

Q0n+1+1=q0qfh+qgkjh=q0n+qcp (6.4.1)

式(6.4.1)和式(6,4.2)中右邊的第二項表示,當觸發器沒有時鐘信號作用時,狀態保持不變。

列出狀態表,列狀態表的方法與同步時序電路分析過程基本相似,只是還應注意各觸發器是否存在吼=1,因此,可在狀態表中增加cp()、cpl兩列。對應于輸人信號C乙K的每一個上升沿,cpO=1,將cp。和FFO的現態Q:代入式(6.4.1),從而得到Q:十1。因為只有對應于O0由0到1的跳變,才有印1=1,而對應于Qo由1到0的轉換9吼=0,所以在每一次0。的狀態轉換后,應首先根據FF1時鐘信號的邏輯表達式確定cp1,然后將FF1的現態Ol和相應的cp1代入式(6.4.2),求得其次態o:+1。如果從0IQ:為00開始推導,可以得到如表6.4,1所示的狀態表。

畫出狀態圖和時序圖

由表6.4.1所示的狀態表可畫出如圖6.4.2所示的狀態圖。

狀態不確定

圖6.4.2 例6.4.1的狀態圖 圖6.4.3 例6.4.1的時序圖

根據狀態圖和具體觸發器的傳輸延遲時間rpLH和莎pHL’可以畫出時序圖,如圖6.4.3所示。可以看出,由于兩個觸發器異步翻轉之間存在延遲,電路有短時間存在著不確定的狀態,如果使用74HCT74雙D觸發器實現圖6.4.1所示.

公網安備44030402000607

公網安備44030402000607