JRW044V(TE1)電路的完全狀態表

發布時間:2019/10/17 21:46:13 訪問次數:1093

JRW044V(TE1)所示的電路,這段時間大約在40ns左右。

邏輯功能分析,由狀態圖和時序圖可知,該電路是一個異步二進制減計數器,z信號的上升沿可觸發借位操作。也可把它看作為一個序列信號發生器。輸出序列脈沖信號z的重復周期為4rcP,脈寬約為1rcP。

例6,4,2 分析圖6,4,4所示邏輯電路。

圖6.4.4 例6.42的邏輯電路圖

解:這是由3個下降沿觸發的r′觸發器構成的異步時序電路G只要相應觸發器的時鐘輸人端CP。出現一次從1到0的跳變,其狀態就會翻轉一次。下面按步驟進行分析。

列出各邏輯方程組

根據邏輯圖列出各觸發器時鐘信號的邏輯表達式

CPO=Q2+C乙Κ=Q2C乙K (6・4.3)

CP1=0。 (6.4,4)

CP2=QOO1+Q2+Cz’Κ=(Q001+Q2)C乙~K (6.4.5)

輸出方程組

即三個觸發器的輸出信號o2、Q1、Q0。

狀態方程組

引人cp″后,r′觸發器的特性方程Q:亠l=0:應改寫為如下狀態方程

0;tl=口lr``()+0l幣T (6・4・6)

0∷1=0{rP】+Ol幣「 (⒍4.7)

0∶+l=口:rP2+Q:幣・I (⒍4.8)

注意:此例中每當CP″發生由1到0的跳變時印″=1。

列出狀態表,從現態o2=o1=G=0開始列狀態表。應從C芭Κ所能觸發的第一個觸發器FF。開始推導其次態。首先確定印0:根據式(⒍4.3),由于Q2=0,C乙Κ信

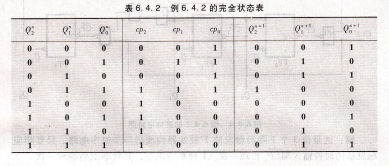

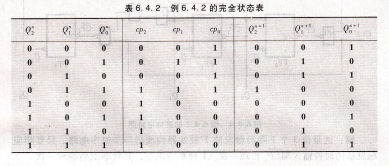

號0→1的跳變必然使CPO產生一個1→0的跳變,所以cpO=1。然后將cP0和現態Ol=0代人式(6.4.6),得到0:+l=1。類似地,根據式(6.4.5),由于O2=Ql=00=0 i CP2為0,此時CLK的任何變化都不會使CP2產生下降沿,故cp2=0,FF2不會改變狀態,o:+l=0。這時9再根據式(6.4.4)確定吼:因為00是0→1跳變,所以cpl=0,Q1也將保持原狀。CLK信號第一個上升沿到來后,電路狀態改變為001。依此類推,可得電路的完全狀態表,如表6.4.2所示。

JRW044V(TE1)所示的電路,這段時間大約在40ns左右。

邏輯功能分析,由狀態圖和時序圖可知,該電路是一個異步二進制減計數器,z信號的上升沿可觸發借位操作。也可把它看作為一個序列信號發生器。輸出序列脈沖信號z的重復周期為4rcP,脈寬約為1rcP。

例6,4,2 分析圖6,4,4所示邏輯電路。

圖6.4.4 例6.42的邏輯電路圖

解:這是由3個下降沿觸發的r′觸發器構成的異步時序電路G只要相應觸發器的時鐘輸人端CP。出現一次從1到0的跳變,其狀態就會翻轉一次。下面按步驟進行分析。

列出各邏輯方程組

根據邏輯圖列出各觸發器時鐘信號的邏輯表達式

CPO=Q2+C乙Κ=Q2C乙K (6・4.3)

CP1=0。 (6.4,4)

CP2=QOO1+Q2+Cz’Κ=(Q001+Q2)C乙~K (6.4.5)

輸出方程組

即三個觸發器的輸出信號o2、Q1、Q0。

狀態方程組

引人cp″后,r′觸發器的特性方程Q:亠l=0:應改寫為如下狀態方程

0;tl=口lr``()+0l幣T (6・4・6)

0∷1=0{rP】+Ol幣「 (⒍4.7)

0∶+l=口:rP2+Q:幣・I (⒍4.8)

注意:此例中每當CP″發生由1到0的跳變時印″=1。

列出狀態表,從現態o2=o1=G=0開始列狀態表。應從C芭Κ所能觸發的第一個觸發器FF。開始推導其次態。首先確定印0:根據式(⒍4.3),由于Q2=0,C乙Κ信

號0→1的跳變必然使CPO產生一個1→0的跳變,所以cpO=1。然后將cP0和現態Ol=0代人式(6.4.6),得到0:+l=1。類似地,根據式(6.4.5),由于O2=Ql=00=0 i CP2為0,此時CLK的任何變化都不會使CP2產生下降沿,故cp2=0,FF2不會改變狀態,o:+l=0。這時9再根據式(6.4.4)確定吼:因為00是0→1跳變,所以cpl=0,Q1也將保持原狀。CLK信號第一個上升沿到來后,電路狀態改變為001。依此類推,可得電路的完全狀態表,如表6.4.2所示。

公網安備44030402000607

公網安備44030402000607