M74HC4051M1R 設計系統的控制單元電路

發布時間:2019/10/25 21:39:35 訪問次數:2189

M74HC4051M1R用Ⅴenlog HDL描述數字統時,可以分為幾種形式?各種描述形式的特點是什么?

數字系統中,通常借助于什么編寫控制單元的Ⅴerilog HDL描述?

比較交通燈控制系統的結構級描述和寄存器傳輸級描述 ,可以得出什么結論?

數字系統的設計方法有兩種:自下而上的設計方法和自上而下的設計方法。現代數字系統的設計常采用自上而下的設計方法。自上而下設計方法的設計步驟是:明確所要設計系統的邏輯功能一→確定實現系統功能的算法,畫出系統方框圖一→設計數據處理單元一)設計控制單元。

ASM圖是數字系統自上而下設計方法中經常采用的設計工具,它是指數字系統控制算法的流程圖,可以將語言描述的設計問題變成時序流程圖的描述,從而獲得狀態函數或輸出函數,得出相應的硬件電路。

寄存器傳輸語言也是數字系統自上而下設計方法中采用的設計工具,它可以將系統技術要求與硬件電路實現之間建立一一對應關系,并能完整地描述數字系統內數據的有序流動和處理.

數字系統的實現方法有多種,這里介紹了采用通用集成邏輯器件和采用可編程邏輯器件兩種方法。采用通用集成邏輯器件是傳統的、成熟的實現方法。采用可編程邏輯器件時,用戶可以將設計的數字系統,用圖形輸入方式或硬件描述語言方式或兩者的混合方式,輸入到開發系統,生成編程用的JE-DEC文件,編程到芯片中.Ⅴer山g HDL是常用的硬件描述語言,采用VerilogHDL可以簡化數字系統的實現過程。

算法狀態機,初始狀態為幾的數字系統,有兩個控制信號X和y,當.Yy=10時,寄存器R加1,系統轉到第二個狀態rl。如果Xy=01時,寄存器R清零,同時系統從幾轉到第三個狀態幾。其他情況下系統處于初始狀態幾。試畫出該數字系統的ASM圖。

一個數字系統的數據處理單元由觸發器E和F、4位二進制計數器為以及必要的門電路組成。計數器的各位為44、A3、A2、A1。系統開始處于初始狀態,當信號s=0時,系統保持在初始狀態;當信號s=1時,計數器⒕和觸發器F清零。從下一個時鐘脈沖開始,計數器進行加1計數,直到系統操作停止。A4和A3的值決定了系統的操作順序。

當A3=0時,觸發器E清零,計數器繼續計數。

當A3=1時,觸發器E置1,并檢測到A4,A4=0時,繼續計數;當A4=1時,觸發器F置1,并停止計數,回到系統初始狀態。

試畫出該系統的ASM圖。

畫出該系統控制單元的狀態圖,并用D觸發器及必要的門電路設計控制單元。

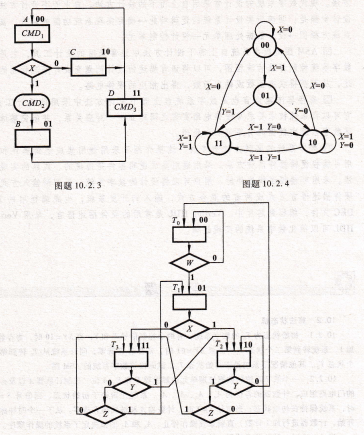

用一個觸發器一個狀態方法實現圖題10.2.3所示的ASM圖。

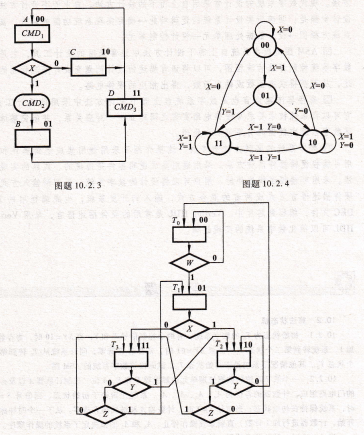

一個數字系統控制單元的狀態圖如圖題10.2.4所示,試畫出等效的ASM圖(狀態框是空的),并用D觸發器和數據選擇器實現控制單元電路。

數字系統的AsM圖如圖題10.2.5所示,試設計系統的控制單元電路。

M74HC4051M1R用Ⅴenlog HDL描述數字統時,可以分為幾種形式?各種描述形式的特點是什么?

數字系統中,通常借助于什么編寫控制單元的Ⅴerilog HDL描述?

比較交通燈控制系統的結構級描述和寄存器傳輸級描述 ,可以得出什么結論?

數字系統的設計方法有兩種:自下而上的設計方法和自上而下的設計方法。現代數字系統的設計常采用自上而下的設計方法。自上而下設計方法的設計步驟是:明確所要設計系統的邏輯功能一→確定實現系統功能的算法,畫出系統方框圖一→設計數據處理單元一)設計控制單元。

ASM圖是數字系統自上而下設計方法中經常采用的設計工具,它是指數字系統控制算法的流程圖,可以將語言描述的設計問題變成時序流程圖的描述,從而獲得狀態函數或輸出函數,得出相應的硬件電路。

寄存器傳輸語言也是數字系統自上而下設計方法中采用的設計工具,它可以將系統技術要求與硬件電路實現之間建立一一對應關系,并能完整地描述數字系統內數據的有序流動和處理.

數字系統的實現方法有多種,這里介紹了采用通用集成邏輯器件和采用可編程邏輯器件兩種方法。采用通用集成邏輯器件是傳統的、成熟的實現方法。采用可編程邏輯器件時,用戶可以將設計的數字系統,用圖形輸入方式或硬件描述語言方式或兩者的混合方式,輸入到開發系統,生成編程用的JE-DEC文件,編程到芯片中.Ⅴer山g HDL是常用的硬件描述語言,采用VerilogHDL可以簡化數字系統的實現過程。

算法狀態機,初始狀態為幾的數字系統,有兩個控制信號X和y,當.Yy=10時,寄存器R加1,系統轉到第二個狀態rl。如果Xy=01時,寄存器R清零,同時系統從幾轉到第三個狀態幾。其他情況下系統處于初始狀態幾。試畫出該數字系統的ASM圖。

一個數字系統的數據處理單元由觸發器E和F、4位二進制計數器為以及必要的門電路組成。計數器的各位為44、A3、A2、A1。系統開始處于初始狀態,當信號s=0時,系統保持在初始狀態;當信號s=1時,計數器⒕和觸發器F清零。從下一個時鐘脈沖開始,計數器進行加1計數,直到系統操作停止。A4和A3的值決定了系統的操作順序。

當A3=0時,觸發器E清零,計數器繼續計數。

當A3=1時,觸發器E置1,并檢測到A4,A4=0時,繼續計數;當A4=1時,觸發器F置1,并停止計數,回到系統初始狀態。

試畫出該系統的ASM圖。

畫出該系統控制單元的狀態圖,并用D觸發器及必要的門電路設計控制單元。

用一個觸發器一個狀態方法實現圖題10.2.3所示的ASM圖。

一個數字系統控制單元的狀態圖如圖題10.2.4所示,試畫出等效的ASM圖(狀態框是空的),并用D觸發器和數據選擇器實現控制單元電路。

數字系統的AsM圖如圖題10.2.5所示,試設計系統的控制單元電路。

公網安備44030402000607

公網安備44030402000607