UCLAMP0501H.TCT共射電路的高頻響應

發布時間:2019/11/6 19:59:32 訪問次數:1172

UCLAMP0501H.TCT簡化為圖4.7.10d的形式,其中C=Cb`e+CM1=Cb`e(1+gmRL)Cb`c。

高頻響應和上限頻率,利用戴維寧定理將圖4.7.10d所示的電路進一步變換為圖4.7,11所示的形式,其中

vs=rbe/rbb+rbevi=rbe/rbe・rb‖rbe/rs+rb‖rbevs,R=rb e‖(rbb`+Rb‖Rs)

圖4.7.11 圖4,7.10d的等效電路

這時只有輸入回路含有電容元件,它與圖4.7.2所示的RC低通電路相似。由此圖及vs與ys的關系,可得圖4.7.10a所示放大電路的高頻源電壓增益的表達式為

avsh=vo/vs・vbe/vs・vs/vs=vo/vbeyo`e=v′s -gm yb`eRL

rb`e Rb‖rbe ArsH=―1=‘jωCrbeRs+Rb‖rbe AvsM≈ArsM (4,7.27)

用Δ♀表示,這里的最大附加相移為一90°,當F=凡時,附加相移Δ♀=-45°。

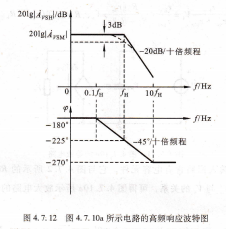

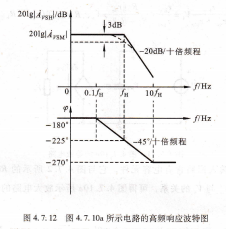

由式(4,7.30)可畫出圖4.7.10a所示共射電路的高頻響應波特圖,如圖4.7.12所示。

201glavsh|/dB201gl/7sM|3dB-20dB/十倍頻程`H-180°-225°`Hz-45-270°

圖4.7.12 圖4.7.10a所示電路的高頻響應波特圖

例4.7.1 設圖4.7.10a所示電路在室溫(300K)下運行,且BJT的7:EQ=0,6V,rbb`=100Ω,`0=100, ‘’b`c=0,5 pF,y.;=400 MHz;ycc=12Ⅴ,Rbl=100 kΩ, 凡2=16 kΩ, Re=1 kΩ, Rc=RI=5.1 kΩ, Rs=1 kΩ, 試計算該電路的中頻源電壓增益及上限頻率。

解:由電路元件參數求得靜態電流為

Rb2=Rbl+R上cQ^上EQ-Re

由式(4,7,13)求得

由式(4.7.12)求得

rb`e=k⊥+`0)若=(1+100)×ui≈2・63 kΩ

由式(4,7.14)求得

gm=O.038S

2π∶2×3.14×400×106 Hz≈15.1 pF

由式(4.7,24b)及(4.7.26b)求得密勒等效電容為

雙極結型三極管及放大電路基礎

≈1 mACM1=(1+gmRL)Cb`c≈49 pF

由式(4.7.28)求得中頻源電壓增益為

圖4.7,11所示等效電路中,輸人回路的等效電阻和等效電容分別為

R=uo|l(rbs.+R;‖R,)≈0・74 kΩ

C=C‘,,+CMl=(15.1+49)pFˉ64.1 PF

自式(4.728)求得上限頻率

ui=2πRc=Ξ×314×o74×lOa(冫×64I×lO 9F≈’・°°批nz

增益一帶寬積,由上述分析可以看出,影響共射極放大電路上限頻率的主要元件及參數是j、w、C蜘和Cm=(1+亂R[〉C忱。因此要提高f※,需選擇i、C1.,小而FT高(C蜘小)的BJT,同時應選用內阻凡小的信號源.此外,還必須減小g。R[,

以減小C,.。的密勒效應。然而,自式(4.728)知,減小g薊Rt必然會使^碼班減

小.可見,r:的提高與^”K的增大是相互矛盾的.對于大多數放大電路而言,都有rl∶>)`1,即通頻帶BⅠ9′=`Ⅱ-yL≈九,因此可以說帶寬與增益是互相制約

的。為綜合考慮這兩方面的性能,弓l出增益一帶寬積這一參數,定義為中頻增

益與帶寬的乘積.對于圖4.7,10a所示電路,其增益-帶寬積可由式(4.7.28)和(4.7.29)相乘獲得,即

|^'si・o|=iR[rbe Rs+Rb‖rbe

2π[廠b`e‖(rbb`+Rb‖R5)][Cb`e+(1+gmRt)cb`c]

當Rb>Rs及Rbrbe時,有

當BJT電路參數如例4.7.1所設時,圖4.7.10a所示電路的|A vsM・o|=65×3.36 MHz≈218.4 MHz。式(4.7.31)說明,在BJT及電路參數都選定后,增益一帶寬積基本上是個常數,即通帶增益要增大多少倍,其帶寬就要變窄多少倍。因而選擇電路參數時,例如負載電阻RL,必須兼顧|sM|和凡的要求。

低頻響應,在低頻范圍內,BJT的極間電容可視為開路,而電路中的耦合電容、旁路電容的電抗增大,不能再視其為短路。據此可畫出圖4.7.10a電路的低頻小信

o 169放大電路的頻率響應.

入觸發器而實現同步預置;當PE=1時,右邊的與門打開,各D觸發器與相應的同或門實現r觸發器功能,接收同步計數的控制信號,其工作原理與圖6.5.11所示電路相同。

表6.5.6所示是74LVC161的功能表。下面對照邏輯圖和功能表,說明它出為高電平,其余均為低電平。

時鐘脈沖CP 是計數脈沖輸人端,也是芯片內4個觸發器的公共時鐘輸人端。

異步清零CR 當它為低電平時,無論其他輸入端是何狀態(包括時鐘信號cP),都使片內所有觸發器狀態置0,稱為異步清零。CR有優先級最高的控制權。下述各輸人信號都是在CR=1時才起作用。

并行置數使能PE 置數控制端。只需在CP上升沿之前保持低電平,數據輸入端D3~DO的邏輯值便能在CP上升沿到來后置人片內4個相應觸發器中。由于該操作與CP上升沿同步,且D3~DO的數據同時置入計數器,所以稱為同步并行預置。為保證數據正確置入,要求PE在CP上升沿之前建立穩定的低電平,其最短提前時間稱為建立時間莎sv,它們時序關系如圖6,5.14(a)。PE置數操作具有次高優先級,僅低于CR,計數和保持操作時都要求PE=1。

數據輸入端DⅣ(D3~DO) 在CP上升沿到來前至少提前砂st將預置數據擺在D3~D。輸入端,且PE=0,則CP上升沿到來后,D3~DO便置人觸發器。該時序與5.3.4節中所述D觸發器相似。CP上升沿對DⅣ的時序要求亦如圖6.5.14(a)所示。

計數使能CEP 只要在CP上升沿到來前至少一個建立時間藝sr期間內保持高電平,且CEr=1,cP上升沿就能使計數器進行一次計數操作。它與CP上升沿的時序關系如圖6.5.14(b)所示。CEP主要控制本芯片的計數操作。

UCLAMP0501H.TCT簡化為圖4.7.10d的形式,其中C=Cb`e+CM1=Cb`e(1+gmRL)Cb`c。

高頻響應和上限頻率,利用戴維寧定理將圖4.7.10d所示的電路進一步變換為圖4.7,11所示的形式,其中

vs=rbe/rbb+rbevi=rbe/rbe・rb‖rbe/rs+rb‖rbevs,R=rb e‖(rbb`+Rb‖Rs)

圖4.7.11 圖4,7.10d的等效電路

這時只有輸入回路含有電容元件,它與圖4.7.2所示的RC低通電路相似。由此圖及vs與ys的關系,可得圖4.7.10a所示放大電路的高頻源電壓增益的表達式為

avsh=vo/vs・vbe/vs・vs/vs=vo/vbeyo`e=v′s -gm yb`eRL

rb`e Rb‖rbe ArsH=―1=‘jωCrbeRs+Rb‖rbe AvsM≈ArsM (4,7.27)

用Δ♀表示,這里的最大附加相移為一90°,當F=凡時,附加相移Δ♀=-45°。

由式(4,7.30)可畫出圖4.7.10a所示共射電路的高頻響應波特圖,如圖4.7.12所示。

201glavsh|/dB201gl/7sM|3dB-20dB/十倍頻程`H-180°-225°`Hz-45-270°

圖4.7.12 圖4.7.10a所示電路的高頻響應波特圖

例4.7.1 設圖4.7.10a所示電路在室溫(300K)下運行,且BJT的7:EQ=0,6V,rbb`=100Ω,`0=100, ‘’b`c=0,5 pF,y.;=400 MHz;ycc=12Ⅴ,Rbl=100 kΩ, 凡2=16 kΩ, Re=1 kΩ, Rc=RI=5.1 kΩ, Rs=1 kΩ, 試計算該電路的中頻源電壓增益及上限頻率。

解:由電路元件參數求得靜態電流為

Rb2=Rbl+R上cQ^上EQ-Re

由式(4,7,13)求得

由式(4.7.12)求得

rb`e=k⊥+`0)若=(1+100)×ui≈2・63 kΩ

由式(4,7.14)求得

gm=O.038S

2π∶2×3.14×400×106 Hz≈15.1 pF

由式(4.7,24b)及(4.7.26b)求得密勒等效電容為

雙極結型三極管及放大電路基礎

≈1 mACM1=(1+gmRL)Cb`c≈49 pF

由式(4.7.28)求得中頻源電壓增益為

圖4.7,11所示等效電路中,輸人回路的等效電阻和等效電容分別為

R=uo|l(rbs.+R;‖R,)≈0・74 kΩ

C=C‘,,+CMl=(15.1+49)pFˉ64.1 PF

自式(4.728)求得上限頻率

ui=2πRc=Ξ×314×o74×lOa(冫×64I×lO 9F≈’・°°批nz

增益一帶寬積,由上述分析可以看出,影響共射極放大電路上限頻率的主要元件及參數是j、w、C蜘和Cm=(1+亂R[〉C忱。因此要提高f※,需選擇i、C1.,小而FT高(C蜘小)的BJT,同時應選用內阻凡小的信號源.此外,還必須減小g。R[,

以減小C,.。的密勒效應。然而,自式(4.728)知,減小g薊Rt必然會使^碼班減

小.可見,r:的提高與^”K的增大是相互矛盾的.對于大多數放大電路而言,都有rl∶>)`1,即通頻帶BⅠ9′=`Ⅱ-yL≈九,因此可以說帶寬與增益是互相制約

的。為綜合考慮這兩方面的性能,弓l出增益一帶寬積這一參數,定義為中頻增

益與帶寬的乘積.對于圖4.7,10a所示電路,其增益-帶寬積可由式(4.7.28)和(4.7.29)相乘獲得,即

|^'si・o|=iR[rbe Rs+Rb‖rbe

2π[廠b`e‖(rbb`+Rb‖R5)][Cb`e+(1+gmRt)cb`c]

當Rb>Rs及Rbrbe時,有

當BJT電路參數如例4.7.1所設時,圖4.7.10a所示電路的|A vsM・o|=65×3.36 MHz≈218.4 MHz。式(4.7.31)說明,在BJT及電路參數都選定后,增益一帶寬積基本上是個常數,即通帶增益要增大多少倍,其帶寬就要變窄多少倍。因而選擇電路參數時,例如負載電阻RL,必須兼顧|sM|和凡的要求。

低頻響應,在低頻范圍內,BJT的極間電容可視為開路,而電路中的耦合電容、旁路電容的電抗增大,不能再視其為短路。據此可畫出圖4.7.10a電路的低頻小信

o 169放大電路的頻率響應.

入觸發器而實現同步預置;當PE=1時,右邊的與門打開,各D觸發器與相應的同或門實現r觸發器功能,接收同步計數的控制信號,其工作原理與圖6.5.11所示電路相同。

表6.5.6所示是74LVC161的功能表。下面對照邏輯圖和功能表,說明它出為高電平,其余均為低電平。

時鐘脈沖CP 是計數脈沖輸人端,也是芯片內4個觸發器的公共時鐘輸人端。

異步清零CR 當它為低電平時,無論其他輸入端是何狀態(包括時鐘信號cP),都使片內所有觸發器狀態置0,稱為異步清零。CR有優先級最高的控制權。下述各輸人信號都是在CR=1時才起作用。

并行置數使能PE 置數控制端。只需在CP上升沿之前保持低電平,數據輸入端D3~DO的邏輯值便能在CP上升沿到來后置人片內4個相應觸發器中。由于該操作與CP上升沿同步,且D3~DO的數據同時置入計數器,所以稱為同步并行預置。為保證數據正確置入,要求PE在CP上升沿之前建立穩定的低電平,其最短提前時間稱為建立時間莎sv,它們時序關系如圖6,5.14(a)。PE置數操作具有次高優先級,僅低于CR,計數和保持操作時都要求PE=1。

數據輸入端DⅣ(D3~DO) 在CP上升沿到來前至少提前砂st將預置數據擺在D3~D。輸入端,且PE=0,則CP上升沿到來后,D3~DO便置人觸發器。該時序與5.3.4節中所述D觸發器相似。CP上升沿對DⅣ的時序要求亦如圖6.5.14(a)所示。

計數使能CEP 只要在CP上升沿到來前至少一個建立時間藝sr期間內保持高電平,且CEr=1,cP上升沿就能使計數器進行一次計數操作。它與CP上升沿的時序關系如圖6.5.14(b)所示。CEP主要控制本芯片的計數操作。

上一篇:S5KC20R低頻小信號等效電路

公網安備44030402000607

公網安備44030402000607