XC3064L-8TQG144I Ҫ^ҫүДzҺ§әНҹбҝsМЧ№Ь

°lІј•rйg:2020/1/7 21:57:33 ФLҶ–ҙО”ө:1064

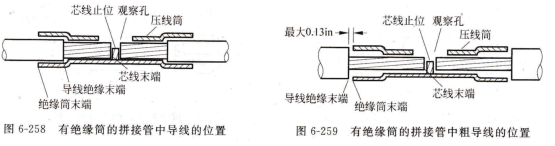

XC3064L-8TQG144IҢўИҘіэҪ^ҫүҢУөДҢ§ҫҖ·ЕИЛЖҙҪУ№Ь,ҷzІйҢ§ҫҖФЪЖҙҪУ№ЬғИөДО»ЦГ,ИзҲD6-258әНҲD6-259ЛщКҫЎЈ

ЖҙҪУ№ЬүәҪУНкіЙәу,ФЪЖҙҪУ№ЬЙПАpА@ғЙҢУҪ^ҫүДzҺ§,өЪТ»ҢУҪ^ҫүДzҺ§ҫoҫoөШАpА@ФЪЖҙҪУ№ЬЙП,ҙ_ұЈДzҺ§Д©¶ЛҙуУЪЖҙҪУ№ЬғЙӮИД©¶ЛЧоЙЩ0.6~0.85in,ДzҺ§АpА@•rЧоРЎЦШҜB50%;өЪТ»ҢУҪ^ҫүДzҺ§АpА@әу,ФЩДж•rбҳҫoҫoөШАpА@өЪ¶юҢУҪ^ҫүДzҺ§,өЪТ»ҢУДzҺ§өДҪKьcҫНКЗөЪ¶юҢУөДЖрьc,өЪ¶юҢУөДҪKьcҫНКЗөЪТ»ҢУЖрьc,ДzҺ§АpА@•rЧоРЎЦШҜB50%ЎЈ

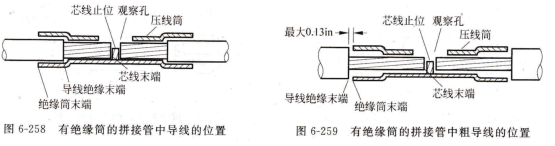

Яx“сәПЯmңШ¶ИөИјүөДҪ^ҫүДzҺ§әНҹбҝsМЧ№Ь,ҙ_ұЈәПҪрЖҙҪУ№ЬөДЧоҙуЦұҸҪФЪҹбҝsМЧ№ЬөДКХҝs·¶ҮъЦ®ғИЎЈҪШИЎәПЯmөДҹбҝsМЧ№ЬйL¶И,ҹбҝsМЧ№ЬЙміцЖҙҪУ№ЬД©¶ЛЧоЙЩ1.1inЎЈҢў·АЧoНкіЙөДЖҙҪУ№Ь·ЕЦГФЪҹбҝsМЧ№ЬЦРРД,К№УГҹбҝs№ӨҫЯНкіЙҹбҝs№ӨЧчЎЈ

ЖҙҪУ№ЬФЪҳЛңКҫҖВ·К©№ӨКЦғФөДІйХТЈ¬ФЪҫSЧoҷzІй№ӨЧчЦР°l¬FТ»јЬІЁТфB737-800пwҷCс{сӮЕ“P6°еЙПУРТ»ёщҢ§ҫҖіц¬FҮАЦШ“pүД,Я@ёщҢ§ҫҖЯBҪУC786Мшй_кPөД=LҪK¶ЛөҪІеЧщD4082oJөД6М–ҝЧО»,Ң§ҫҖйL¶ИҝЙТФФЩЧцТ»ҙОУАҫГРЮАн,Ң§ҫҖҳЛЧRКЗo224-24;УЙУЪЯ@ёщҢ§ҫҖО»УЪс{сӮЕ“,ҝЙЗ§ІоИf„e,ө«ЛьӮғИФУР№ІН¬Ц®МҺ,КЗТ»°гCPLDЖчјюөДҪYҳӢҝтҲDЎЈЖдЦРЯүЭӢүKўЩҫНПа®”УЪТ»ӮҖGALЖчјю(ТҠ6,7№қ),CPLDЦРУР¶аӮҖЯүЭӢүK,Я@Р©ЯүЭӢүKЦ®йgҝЙТФК№УГҝЙҫҺіМғИІҝЯBҫҖҢҚ¬FПа»ҘЯBҪУЎЈһйБЛФцҸҠҢҰI/0өДҝШЦЖДЬБҰ,МбёЯТэД_өДЯm‘ӘРФ,CPLDЦРЯҖФцјУБЛI/oҝШЦЖүKЎЈГҝӮҖI/0үKЦРУРИфёЙӮҖI/oҶОФӘЎЈ

ҝЙҫҺіМіЛ·eн—кҮ,іЛ·eн—кҮБРУРгбӮҖЭ”Ил,ҝЙТФ®aЙъ¶шЧғБҝөДіЛ·eн—ЎЈТ»°гТ»ӮҖәкҶОФӘҢҰ‘Ә5ӮҖіЛ·eн—,Я@ҳУ,ФЪЯүЭӢүKЦР№ІУР5ЎБЖЁӮҖіЛ·eн—ЎЈАэИз,XC9500ПөБРөДЯүЭӢүKЦРУР90ӮҖ36ЧғБҝіЛ·eн—,MAX7000ПөБРөДЯүЭӢүKЦРУР80ӮҖ36ЧғБҝіЛ·eн—ЎЈ

іЛ·eн—·ЦЕдәНәкҶОФӘ,І»Н¬РНМ–өДCPLDЖчјю,іЛ·eн—·ЦЕдәНәкҶОФӘлҠВ·ҪYҳӢТІІ»НкИ«ПаН¬,ө«ЛщТӘҢҚ¬FөД№ҰДЬҙууwПаЛЖЎЈһйXC9500ПөБРөДіЛ·eн—·ЦЕдәНәкҶОФӘлҠВ·ЎЈҲDЦРS1~S:һйҝЙҫҺіМ”ө“ю·ЦЕдЖч,M1~M5һйҝЙҫҺіМ”ө“юЯx“сЖчЎЈһйәҶГчЖрТҠ,ӣ]УР®ӢіцЛьӮғөДҝЙҫҺіМЯx“сЭ”Ил¶ЛЎЈ

»тПВТ»ӮҖәкҶОФӘИҘЎЈЯ@·NіЛ·eн—өДЎ°жңКҪЎұҪYҳӢ,ҝЙТФҢҚ¬FЯhЯh¶аУЪ5ӮҖіЛ·eн—өДЕcТ»»тКҪЎЈФЪXC9500ПөБРCPLDЦР,АнХ“ЙПҝЙТФҢў90ӮҖіЛ·eн—ҪMәПөҪТ»ӮҖәкҶОФӘЦР,®aЙъ90ӮҖіЛ·eн—өДЕcТ»»тКҪ,ө«ҙЛ•rЖдУа17ӮҖәкҶОФӘҢўІ»ДЬК№УГіЛ·eн—БЛЎЈФЪAltera№«ЛҫЙъ®aөДCPLDЦР,әкҶОФӘЦРіэБЛУРіЛ·eн—”UХ№№ҰДЬНв,ЯҖУРіЛ·eн—№ІПнлҠВ·,К№өГН¬Т»ӮҖіЛ·eн—ҝЙТФұ»¶аӮҖәкҶОФӘН¬•rК№УГЎЈ

”ө“ю·ЦЕдЖчS1~S5ЦРйgЭ”іцөДіЛ·eн—УГУЪМШКв№ҰДЬ,Я@Р©№ҰДЬ°ьАЁЧчһйУ|°lЖчFFөДЦГО»ЎўҸНО»Ўў•rзҠРЕМ–,®җ»тйTG5өДН¬Па/·ҙПаЭ”іцҝШЦЖРЕМ–әНіЛ·eн—Э”іцК№ДЬҝШЦЖРЕМ–PrOEЎЈ

»тйTG4Э”іцөДЕcТ»»тКҪЛНЦБ®җ»тйTG5,G5өДБнТ»Э”ИлҒнЧФ”ө“юЯx“сЖчM1ЎЈНЁЯ^ҢҰM1өДҫҺіМ,ҝЙТФЯx“с0Ўў1»тБнТ»ӮҖіЛ·eн—,ҒнҝШЦЖG4өДЭ”іцҪӣG5КЗ·с·ҙПа,»тКЬБнТ»ӮҖіЛ·eн—ҝШЦЖЎЈM3ҝЙТФЯx“сКЗЦұҪУҪMәПРОКҪЭ”іцЯҖКЗҪӣЯ^У|°lЖчөДјДҙжЖчРОКҪЭ”іц,У|°lЖчFFҝЙТФұ»ҫҺіМһйDУ|°lЖч»тrУ|°lЖч,ЗТНЁЯ^M2әНM5ҝЙТФЯx“сИ«ҫЦ»тіЛ·eн—ЦГО»ЎўҸНО»РЕМ–ЎЈНЁЯ^M4ТІҝЙТФФЪ3ӮҖИ«ҫЦ•rзҠәНТ»ӮҖіЛ·eн—ЦРЯx“сУ|°lЖчөД•rзҠРЕМ–ЎЈ

әкҶОФӘөДЭ”іцІ»ғHЛНЦБI/0ҶОФӘ,ЯҖЛНөҪғИІҝҝЙҫҺіМЯBҫҖ…^,ТФұ»ЖдЛыәкҶОФӘК№УГЎЈ

ЙоЫЪКРОЁУР¶ИҝЖјјУРПЮ№«Лҫhttp://wydkj.51dzw.com/

XC3064L-8TQG144IҢўИҘіэҪ^ҫүҢУөДҢ§ҫҖ·ЕИЛЖҙҪУ№Ь,ҷzІйҢ§ҫҖФЪЖҙҪУ№ЬғИөДО»ЦГ,ИзҲD6-258әНҲD6-259ЛщКҫЎЈ

ЖҙҪУ№ЬүәҪУНкіЙәу,ФЪЖҙҪУ№ЬЙПАpА@ғЙҢУҪ^ҫүДzҺ§,өЪТ»ҢУҪ^ҫүДzҺ§ҫoҫoөШАpА@ФЪЖҙҪУ№ЬЙП,ҙ_ұЈДzҺ§Д©¶ЛҙуУЪЖҙҪУ№ЬғЙӮИД©¶ЛЧоЙЩ0.6~0.85in,ДzҺ§АpА@•rЧоРЎЦШҜB50%;өЪТ»ҢУҪ^ҫүДzҺ§АpА@әу,ФЩДж•rбҳҫoҫoөШАpА@өЪ¶юҢУҪ^ҫүДzҺ§,өЪТ»ҢУДzҺ§өДҪKьcҫНКЗөЪ¶юҢУөДЖрьc,өЪ¶юҢУөДҪKьcҫНКЗөЪТ»ҢУЖрьc,ДzҺ§АpА@•rЧоРЎЦШҜB50%ЎЈ

Яx“сәПЯmңШ¶ИөИјүөДҪ^ҫүДzҺ§әНҹбҝsМЧ№Ь,ҙ_ұЈәПҪрЖҙҪУ№ЬөДЧоҙуЦұҸҪФЪҹбҝsМЧ№ЬөДКХҝs·¶ҮъЦ®ғИЎЈҪШИЎәПЯmөДҹбҝsМЧ№ЬйL¶И,ҹбҝsМЧ№ЬЙміцЖҙҪУ№ЬД©¶ЛЧоЙЩ1.1inЎЈҢў·АЧoНкіЙөДЖҙҪУ№Ь·ЕЦГФЪҹбҝsМЧ№ЬЦРРД,К№УГҹбҝs№ӨҫЯНкіЙҹбҝs№ӨЧчЎЈ

ЖҙҪУ№ЬФЪҳЛңКҫҖВ·К©№ӨКЦғФөДІйХТЈ¬ФЪҫSЧoҷzІй№ӨЧчЦР°l¬FТ»јЬІЁТфB737-800пwҷCс{сӮЕ“P6°еЙПУРТ»ёщҢ§ҫҖіц¬FҮАЦШ“pүД,Я@ёщҢ§ҫҖЯBҪУC786Мшй_кPөД=LҪK¶ЛөҪІеЧщD4082oJөД6М–ҝЧО»,Ң§ҫҖйL¶ИҝЙТФФЩЧцТ»ҙОУАҫГРЮАн,Ң§ҫҖҳЛЧRКЗo224-24;УЙУЪЯ@ёщҢ§ҫҖО»УЪс{сӮЕ“,ҝЙЗ§ІоИf„e,ө«ЛьӮғИФУР№ІН¬Ц®МҺ,КЗТ»°гCPLDЖчјюөДҪYҳӢҝтҲDЎЈЖдЦРЯүЭӢүKўЩҫНПа®”УЪТ»ӮҖGALЖчјю(ТҠ6,7№қ),CPLDЦРУР¶аӮҖЯүЭӢүK,Я@Р©ЯүЭӢүKЦ®йgҝЙТФК№УГҝЙҫҺіМғИІҝЯBҫҖҢҚ¬FПа»ҘЯBҪУЎЈһйБЛФцҸҠҢҰI/0өДҝШЦЖДЬБҰ,МбёЯТэД_өДЯm‘ӘРФ,CPLDЦРЯҖФцјУБЛI/oҝШЦЖүKЎЈГҝӮҖI/0үKЦРУРИфёЙӮҖI/oҶОФӘЎЈ

ҝЙҫҺіМіЛ·eн—кҮ,іЛ·eн—кҮБРУРгбӮҖЭ”Ил,ҝЙТФ®aЙъ¶шЧғБҝөДіЛ·eн—ЎЈТ»°гТ»ӮҖәкҶОФӘҢҰ‘Ә5ӮҖіЛ·eн—,Я@ҳУ,ФЪЯүЭӢүKЦР№ІУР5ЎБЖЁӮҖіЛ·eн—ЎЈАэИз,XC9500ПөБРөДЯүЭӢүKЦРУР90ӮҖ36ЧғБҝіЛ·eн—,MAX7000ПөБРөДЯүЭӢүKЦРУР80ӮҖ36ЧғБҝіЛ·eн—ЎЈ

іЛ·eн—·ЦЕдәНәкҶОФӘ,І»Н¬РНМ–өДCPLDЖчјю,іЛ·eн—·ЦЕдәНәкҶОФӘлҠВ·ҪYҳӢТІІ»НкИ«ПаН¬,ө«ЛщТӘҢҚ¬FөД№ҰДЬҙууwПаЛЖЎЈһйXC9500ПөБРөДіЛ·eн—·ЦЕдәНәкҶОФӘлҠВ·ЎЈҲDЦРS1~S:һйҝЙҫҺіМ”ө“ю·ЦЕдЖч,M1~M5һйҝЙҫҺіМ”ө“юЯx“сЖчЎЈһйәҶГчЖрТҠ,ӣ]УР®ӢіцЛьӮғөДҝЙҫҺіМЯx“сЭ”Ил¶ЛЎЈ

»тПВТ»ӮҖәкҶОФӘИҘЎЈЯ@·NіЛ·eн—өДЎ°жңКҪЎұҪYҳӢ,ҝЙТФҢҚ¬FЯhЯh¶аУЪ5ӮҖіЛ·eн—өДЕcТ»»тКҪЎЈФЪXC9500ПөБРCPLDЦР,АнХ“ЙПҝЙТФҢў90ӮҖіЛ·eн—ҪMәПөҪТ»ӮҖәкҶОФӘЦР,®aЙъ90ӮҖіЛ·eн—өДЕcТ»»тКҪ,ө«ҙЛ•rЖдУа17ӮҖәкҶОФӘҢўІ»ДЬК№УГіЛ·eн—БЛЎЈФЪAltera№«ЛҫЙъ®aөДCPLDЦР,әкҶОФӘЦРіэБЛУРіЛ·eн—”UХ№№ҰДЬНв,ЯҖУРіЛ·eн—№ІПнлҠВ·,К№өГН¬Т»ӮҖіЛ·eн—ҝЙТФұ»¶аӮҖәкҶОФӘН¬•rК№УГЎЈ

”ө“ю·ЦЕдЖчS1~S5ЦРйgЭ”іцөДіЛ·eн—УГУЪМШКв№ҰДЬ,Я@Р©№ҰДЬ°ьАЁЧчһйУ|°lЖчFFөДЦГО»ЎўҸНО»Ўў•rзҠРЕМ–,®җ»тйTG5өДН¬Па/·ҙПаЭ”іцҝШЦЖРЕМ–әНіЛ·eн—Э”іцК№ДЬҝШЦЖРЕМ–PrOEЎЈ

»тйTG4Э”іцөДЕcТ»»тКҪЛНЦБ®җ»тйTG5,G5өДБнТ»Э”ИлҒнЧФ”ө“юЯx“сЖчM1ЎЈНЁЯ^ҢҰM1өДҫҺіМ,ҝЙТФЯx“с0Ўў1»тБнТ»ӮҖіЛ·eн—,ҒнҝШЦЖG4өДЭ”іцҪӣG5КЗ·с·ҙПа,»тКЬБнТ»ӮҖіЛ·eн—ҝШЦЖЎЈM3ҝЙТФЯx“сКЗЦұҪУҪMәПРОКҪЭ”іцЯҖКЗҪӣЯ^У|°lЖчөДјДҙжЖчРОКҪЭ”іц,У|°lЖчFFҝЙТФұ»ҫҺіМһйDУ|°lЖч»тrУ|°lЖч,ЗТНЁЯ^M2әНM5ҝЙТФЯx“сИ«ҫЦ»тіЛ·eн—ЦГО»ЎўҸНО»РЕМ–ЎЈНЁЯ^M4ТІҝЙТФФЪ3ӮҖИ«ҫЦ•rзҠәНТ»ӮҖіЛ·eн—ЦРЯx“сУ|°lЖчөД•rзҠРЕМ–ЎЈ

әкҶОФӘөДЭ”іцІ»ғHЛНЦБI/0ҶОФӘ,ЯҖЛНөҪғИІҝҝЙҫҺіМЯBҫҖ…^,ТФұ»ЖдЛыәкҶОФӘК№УГЎЈ

ЙоЫЪКРОЁУР¶ИҝЖјјУРПЮ№«Лҫhttp://wydkj.51dzw.com/

ЙПТ»ЖӘЈәSA36A-T ҷzІйҢ§ҫҖФЪЖҙҪУ№ЬғИөДО»ЦГ

ЙПТ»ЖӘЈәUC5608NУўЦЖҶОО»өДҢ§№ЬәНҫo№Мјю

ҹбйTьc“ф

ҹбйTьc“ф

- SKT520/20E ҶО·Җ‘BУ|°lЖчөДЧоёЯ№ӨЧч

- AM29DL163DB90PCI јӨІЁК§ЛЩәН

- LT1168CS8PBF №МуwұнГжЯ\„У•r®aЙъ

- SG73P2BTTD3000F ҶО¶ЛЭ”іцөД№І

- UDP411D-1кP”а»тёДЧғИјУНөДБч„УөД·ҪПт

- XO43B16.000MHZ пwҷCҪYҳӢөДЯmәҪ

- FR207G ҝ№ИјРФәвБҝДНИјРФ

- K6R4008V1C-TC20 Л®гyқсКҪЙа»Й

- TC822RCPL ‘Әјұ·ЕУНПөҪyөДЦчТӘёҪјю

- NCP1653DG й_кPЖчјюәН·ҙрҒСУ•rӯh№қ

НЖЛ]јјРgЩYБП

НЖЛ]јјРgЩYБП

- »¬С©А@ҳ¶ҷCЖчИЛ

- ұҫАэКЗТ»ҝо·ЗіЈУРИӨЈ¬Н¬•rУЦУРТ»¶ЁХ{ФҮлy¶ИөДНж·ЁЎЈEDE2116AB... [Ф”јҡ]

- ДЈ”MәН»мәПРЕМ–ЖҪЕ_TreoФ”Зй

- PXIәНLXIДЈүK»ҜҪвӣQ·Ҫ°ёҪвЧx

- AN-13-0004_CANКХ°lЖчҪYҳӢ…ў”өМШ

- ЖБұО–ЕІЫңПјјРg (SGT)&#

- өЪТ»ҙъSGT MOSFETПөБРјјРgҪYҳӢ…ў”ө·в

- И«ЗтКЧоwGSE DPUРҫЖ¬°lІј

- ¶аГҪуw…fМҺАнЖчSM501ФЪЗ¶ИлКҪПөҪyЦРөД‘ӘУГ

- »щУЪIEEE802.11bөДEPAңШ¶ИЧғЛНЖч

- QUICCEngineРВТэЗжНЖ„УIPҫWҪjёпРВ

- SoCГжКА°ЛДкәуөД®aҳIҷCУц

- MPC8xxПөБРМҺАнЖчөДЗ¶ИлКҪПөҪyлҠФҙФOУӢ

- dsPICј°ЖдФЪҪ»БчЧғоlХ{ЛЩЦРөД‘ӘУГСРҫҝ

№«ҫW°ІӮд44030402000607

№«ҫW°ІӮд44030402000607