ad9914bcpz 上拉電阻、下拉電阻和弱保持電路

發布時間:2020/1/16 17:37:46 訪問次數:1165

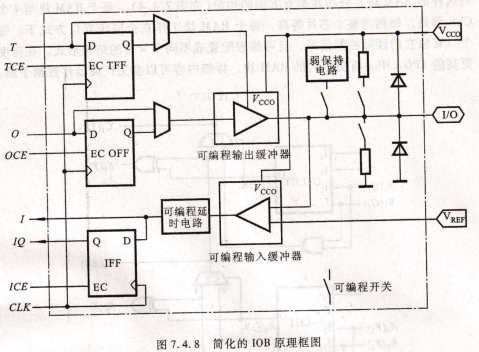

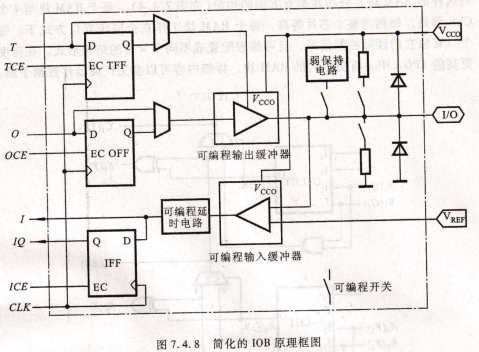

ad9914bcpz簡化的IOB原理框圖作,其最短延遲時間為零,3個觸發器均可編程配置為邊沿觸發或電平觸發方式,它們共用一個時鐘信號CLK,但有各自的時鐘使能控制信號。通過它們可以實現同步輸入/輸出。輸入、輸出緩沖器和IOB中所有的信號,均有獨立的極性控制電路(圖7.4.8中未畫出),可以控制信號是否反相,使能信號是高有效還是低有效,觸發器是上升沿觸發還是下降沿觸發等。

圖7.4.8中兩個鉗位二極管具有瞬時過壓保護和靜電保護作用。上拉電阻、下拉電阻和弱保持電路(Weak keeper Circuit)可通過編程配置給I/o引腳。弱保持電路監視并跟蹤1/0引腳輸入電壓的變化,當連至引腳總線上所有的驅動信號全部無效時,弱保持電路將維持在引腳最后一個狀態的邏輯電平上,可以避免總線處于懸浮狀態,消除總線抖動。

為使FPGA能在不同電源系統中正常工作,IOB中設計了兩個電壓輸入端Vcc。和ⅤRm(它們由多個IOB共用)。VRⅢ為邏輯電平的參考電壓,在執行某些I/0標準時,需要輸人ⅤREF①。大約每6個I/o有一個VREF引腳。在此基礎上,為了增強FPGA的適應性和靈活性,將若干個IOB組織在一起,構成一個組(Bank),如圖7.4,9所示。一般FPGA的I/o劃分為8個詳見廠商數據手冊,存儲器、復雜可編程器件和明場可編程門陣列.

0FF可編程輸出緩沖進位到相鄰的GRM,到相鄰的GRM,每個開關矩陣中的6路開關管,圖7.4.11 GRM的結構.

I/0布線資源,在CLB陣列與10B接口的外圍,有附加的布線資源,稱為萬能環(Ⅴer~saRing)。通過對這些布線資源的編程,可以方便地實現引腳的交換和鎖定。使引腳位置的變動與內部邏輯無關。

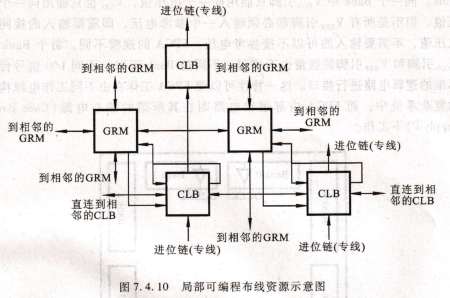

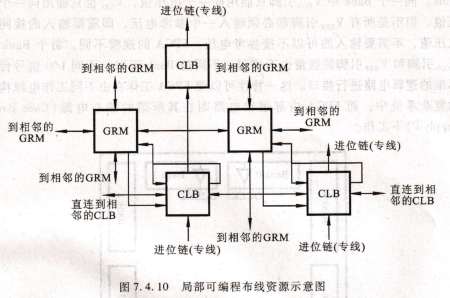

專用布線資源,除了以上布線資源,FPGA中還包含具有特殊用途的橫向片內三態總線和縱向進位鏈(如圖7,4.10)的專用布線資源。

存儲器、復雜可編程器件,和現場可編程閘,到相鄰的GRM進位鏈(專線).

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

ad9914bcpz簡化的IOB原理框圖作,其最短延遲時間為零,3個觸發器均可編程配置為邊沿觸發或電平觸發方式,它們共用一個時鐘信號CLK,但有各自的時鐘使能控制信號。通過它們可以實現同步輸入/輸出。輸入、輸出緩沖器和IOB中所有的信號,均有獨立的極性控制電路(圖7.4.8中未畫出),可以控制信號是否反相,使能信號是高有效還是低有效,觸發器是上升沿觸發還是下降沿觸發等。

圖7.4.8中兩個鉗位二極管具有瞬時過壓保護和靜電保護作用。上拉電阻、下拉電阻和弱保持電路(Weak keeper Circuit)可通過編程配置給I/o引腳。弱保持電路監視并跟蹤1/0引腳輸入電壓的變化,當連至引腳總線上所有的驅動信號全部無效時,弱保持電路將維持在引腳最后一個狀態的邏輯電平上,可以避免總線處于懸浮狀態,消除總線抖動。

為使FPGA能在不同電源系統中正常工作,IOB中設計了兩個電壓輸入端Vcc。和ⅤRm(它們由多個IOB共用)。VRⅢ為邏輯電平的參考電壓,在執行某些I/0標準時,需要輸人ⅤREF①。大約每6個I/o有一個VREF引腳。在此基礎上,為了增強FPGA的適應性和靈活性,將若干個IOB組織在一起,構成一個組(Bank),如圖7.4,9所示。一般FPGA的I/o劃分為8個詳見廠商數據手冊,存儲器、復雜可編程器件和明場可編程門陣列.

0FF可編程輸出緩沖進位到相鄰的GRM,到相鄰的GRM,每個開關矩陣中的6路開關管,圖7.4.11 GRM的結構.

I/0布線資源,在CLB陣列與10B接口的外圍,有附加的布線資源,稱為萬能環(Ⅴer~saRing)。通過對這些布線資源的編程,可以方便地實現引腳的交換和鎖定。使引腳位置的變動與內部邏輯無關。

專用布線資源,除了以上布線資源,FPGA中還包含具有特殊用途的橫向片內三態總線和縱向進位鏈(如圖7,4.10)的專用布線資源。

存儲器、復雜可編程器件,和現場可編程閘,到相鄰的GRM進位鏈(專線).

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607