ad9434bcpz-500 進出CLB信號的連線資源

發布時間:2020/1/16 17:41:09 訪問次數:1821

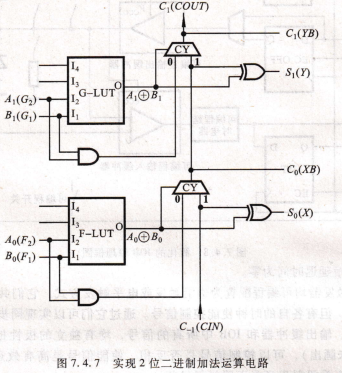

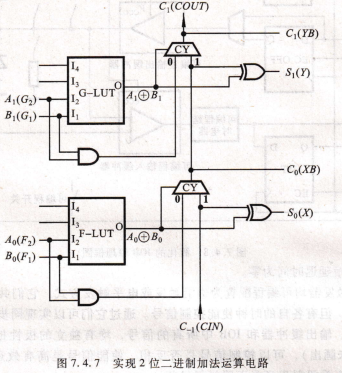

ad9434bcpz-500實現2位二進制加法運算電路,輸入/輸出模塊lOB,IOB是FPGA外部封裝引腳和內部邏輯間的接口。每個IOB對應一個封裝引腳,通過對IOB編程,可將引腳分別定義為輸入、輸出和雙向功能。IOB的簡化原理圖如圖7.4.7所示。圖中的Ⅴcc。和ⅤREF引腳與其他IOB共用。IOB中有輸人和輸出兩條信號通路。當I/0引腳用作輸出時,內部邏輯信號由@端進人IOB模塊,由可編程數據選擇器確定是直接送輸出緩沖器還是經過D觸發器寄存后再送輸出緩沖器。輸出緩沖器使能控制信號r可以直接控制輸出緩沖器,也可以通過觸發器TFF后再控制輸出緩沖器。當I/0引腳用作輸入時,引腳上的輸人信號經過輸入緩沖器,可以直接由J進人內部邏輯電路,也可以經觸發器IFF寄存后由四輸人到內部邏輯電路中。沒有用到的引腳被預置為高阻態。

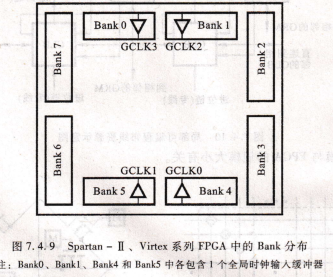

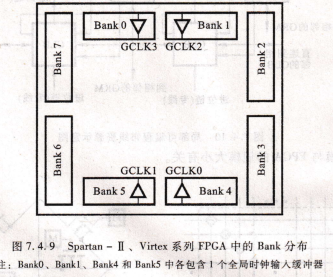

可編程延時電路可以控制輸入信號進人的時機,保證內部邏輯電路協調工Bank。同一個Bank中Ⅴcc。引腳只能用同一個電壓值,VRm也只能用同一個電壓值。但不是所有VREF引腳都必須輸人一個參考電壓,即需要輸入的接同一電壓值,不需要輸入的可以不接參考電壓。FPGA的規模不同,每個Bank中Vcc。引腳和VRm引腳的數量也不相同。不同的Bank可以與不同I/0信號傳輸標準的邏輯電路進行接口。這一特性可以使FPGA工作在由不同工作電源構成的復雜系統中,而FPGA內部邏輯電路則在其所謂的核心電源(Core Powersupply①)下工作。

圖7.4.9 spartan-Ⅱ、Virtex系列FPGA中的Bank分布

注:BankO、Bank1、Bank4和Bank5中各包含1個全局時鐘輸人緩沖器

可編程布線資源,FPGA中有多種布線資源,包括局部布線資源、通用布線資源、I/0布線資源、專用布線資源和全局布線資源等,它們分別承擔了不同的連線任務。

局部布線資源,局部布線資源是指進出CLB信號的連線資源,其示意圖如圖7,4.10所示。其中GRM②為通用布線矩陣。局部布線資源主要包括三部分連接:CLB到GRM之間的連接;CLB的輸出到自身輸人的高速反饋連接;CLB到水平相鄰CLB間的直通快速連接,避免了通過GRM產生的延時。

通用布線區,通用布線區由GRM及其連線構成。GRM是行線資源與列線資源互聯的開關矩陣,其結構如圖7.4.11所示。通用布線區是FPGA中主要的內連資源。

xilinx公司的FPGA芯片以VccNT標注。

系General Rouung Matnx的縮寫,現場可編程閘陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

ad9434bcpz-500實現2位二進制加法運算電路,輸入/輸出模塊lOB,IOB是FPGA外部封裝引腳和內部邏輯間的接口。每個IOB對應一個封裝引腳,通過對IOB編程,可將引腳分別定義為輸入、輸出和雙向功能。IOB的簡化原理圖如圖7.4.7所示。圖中的Ⅴcc。和ⅤREF引腳與其他IOB共用。IOB中有輸人和輸出兩條信號通路。當I/0引腳用作輸出時,內部邏輯信號由@端進人IOB模塊,由可編程數據選擇器確定是直接送輸出緩沖器還是經過D觸發器寄存后再送輸出緩沖器。輸出緩沖器使能控制信號r可以直接控制輸出緩沖器,也可以通過觸發器TFF后再控制輸出緩沖器。當I/0引腳用作輸入時,引腳上的輸人信號經過輸入緩沖器,可以直接由J進人內部邏輯電路,也可以經觸發器IFF寄存后由四輸人到內部邏輯電路中。沒有用到的引腳被預置為高阻態。

可編程延時電路可以控制輸入信號進人的時機,保證內部邏輯電路協調工Bank。同一個Bank中Ⅴcc。引腳只能用同一個電壓值,VRm也只能用同一個電壓值。但不是所有VREF引腳都必須輸人一個參考電壓,即需要輸入的接同一電壓值,不需要輸入的可以不接參考電壓。FPGA的規模不同,每個Bank中Vcc。引腳和VRm引腳的數量也不相同。不同的Bank可以與不同I/0信號傳輸標準的邏輯電路進行接口。這一特性可以使FPGA工作在由不同工作電源構成的復雜系統中,而FPGA內部邏輯電路則在其所謂的核心電源(Core Powersupply①)下工作。

圖7.4.9 spartan-Ⅱ、Virtex系列FPGA中的Bank分布

注:BankO、Bank1、Bank4和Bank5中各包含1個全局時鐘輸人緩沖器

可編程布線資源,FPGA中有多種布線資源,包括局部布線資源、通用布線資源、I/0布線資源、專用布線資源和全局布線資源等,它們分別承擔了不同的連線任務。

局部布線資源,局部布線資源是指進出CLB信號的連線資源,其示意圖如圖7,4.10所示。其中GRM②為通用布線矩陣。局部布線資源主要包括三部分連接:CLB到GRM之間的連接;CLB的輸出到自身輸人的高速反饋連接;CLB到水平相鄰CLB間的直通快速連接,避免了通過GRM產生的延時。

通用布線區,通用布線區由GRM及其連線構成。GRM是行線資源與列線資源互聯的開關矩陣,其結構如圖7.4.11所示。通用布線區是FPGA中主要的內連資源。

xilinx公司的FPGA芯片以VccNT標注。

系General Rouung Matnx的縮寫,現場可編程閘陣列.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607