LG631-9R加法運算涉及進位問題

發布時間:2020/1/16 18:01:24 訪問次數:850

延時鎖環DLL可以控制和修正內部各部分時鐘的傳輸延遲時間,保證邏輯電路可靠地工作。同時,也可以產生相位滯后0°、90°、180°和270°的時鐘脈沖,還可產生倍頻或分頻時鐘,分頻系數可以是1.5、2、2.5、3、4、5、8、16等。

CLB之間的空隙部分是布線區①,分布著可編程布線資源。通過它們實現CLB與CLB之間、CLB與IOB之間以及全局時鐘等信號與CLB和IOB之間的連接。

在Xilinx公司的高性能產品中,已將乘法器、數字信號處理器等集成在FPGA中,大大增強了FPGA的功能。同時,為了使芯片穩定可靠地工作,其內部都設有數字時鐘管理模塊。由于這些內容已超出本書討論范圍,所以此處只介紹FPGA中幾個最基本的功能模塊。

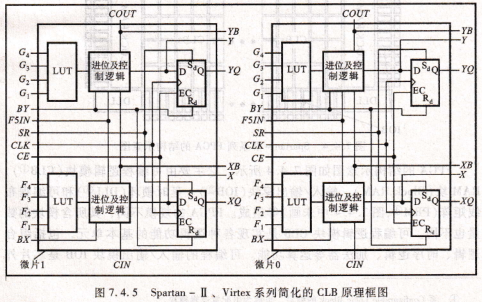

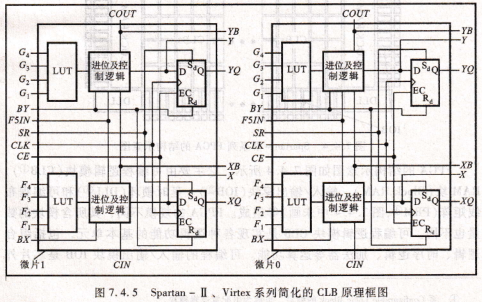

可編程邏輯模塊CLB,CLB是FPGA中的基本邏輯模塊,它可實現絕大多數的邏輯功能,其簡化的原理框圖如圖7.4.5所示。構成CLB的基礎是邏輯單元(LC②),一個LC中包括一個4輸人LUT、進位及控制邏輯和一個D觸發器(EC為時鐘使能控制端)。每個CLB包含4個LC,并將每2個LC組織在1個微片(slice)中,圖中可見有2個微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4個微片,即含有8個LC。CLB的輸入來自可編程布線區,其輸出再回送到內部布線區。

圖7.4.5 Spartan-Ⅱ、Ⅴirtex系列簡化的CLB原理框圖

實際上,「PGA采用多層布局布線結構,并非只能在模塊間的空隙處布線。

Logic Cell的縮寫,存儲器、復雜可編程器件和明場可編程門陣列.

來自CLB以外布線區的4個輸入變量同時送人F1~F4和相應的C1~C4,第5個輸入變量送至BX端。F-LUT、G-LUT的輸出和BX經數據選擇器F5擴展為5變量邏輯函數。該結果可直接由F5端輸出,也可經XMUX、DXMUX和D觸發器,由X和/或X0端輸出。

實現6變量任意邏輯函數,實現6變量任意邏輯函數需用2個微片。在實現5變量函數基礎上,將另一個微片的乃的輸出送入此微片的F5JⅣ輸人端,第6個變量送人By端。數據選擇器F5的輸出、F5JⅣ和By經數據選擇器F6擴展為6變量邏輯函數。該結果經YMUX、DYMUX和D觸發器,由y和/或yQ端輸出。

2位二進制加法器,由于加法運算涉及進位問題,所以CLB中專門設計了進位鏈,一個微片可以完成2位二進制數的加法運算。實現加法運算時,加數A1A。和被加數B1BO分別送入G2F2和G1F1,即C2=A1,Cl=B1,F2=A0,F1=BO。通過編程使兩個LUT分別實現F2①F1和C2①C1,同時編程使XMUx和YMUX選通異或門的輸出,使xCMUX和YCMUX選通與門的輸出,使YBMUX選通上端CY的輸出。這樣,圖7.4,6可以簡化為圖7.4.7的形式。其中,低位的和So=A0①BO①Ci,進位Co為Co=(Ao①Bo)AOBO+(Ao①BO)C~1=(AOBo+AOBO)AOBO+(Ao①Bo)C~1=AoBO+(Ao∈)Bo)C~1

高位的和及進位有相同的結果,由此看出,電路上、下兩部分分別為兩個全加器。

圖7.4.6所示電路中的與門、ⅩCMUX、YCMUX、C~1^MUX和CY構成進位邏輯電路,也稱進位鏈,可以與其他微片串聯實現更多位的加法運算。當此微片為最低位時,通過編程使C~1MUX選通BX,且使Bx二0。

時序邏輯的實現,圖7.4.6中觸發器的輸出,經布線區反饋給輸人,再經LUT產生激勵函數驅動觸發器的D端,從而構成時序邏輯電路。觸發器的激勵函數也可通過DXMUX(DYMUX)直接取自BX(By)。由多個CLB便可構成復雜的時序邏輯電路。

由于LUT就是一個16×1位的SRAM,所以CLB也可用來作存儲器使用,不過此時LUT中的內容不再是預先配置好的,而是在正常工作時可以隨時讀寫的,而且LUT不能再作為邏輯函數產生器使用。LUT也可以被設置成16位移位寄存器使用。另外,為彌補LUT構成RAM在容量上的不足,在FPGA中還增加了RAM塊。這些RAM塊以列的形式排列,在Spartan-Ⅱ系列中有兩存儲器、復雜可編程器件利現場可編程閘陣.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

延時鎖環DLL可以控制和修正內部各部分時鐘的傳輸延遲時間,保證邏輯電路可靠地工作。同時,也可以產生相位滯后0°、90°、180°和270°的時鐘脈沖,還可產生倍頻或分頻時鐘,分頻系數可以是1.5、2、2.5、3、4、5、8、16等。

CLB之間的空隙部分是布線區①,分布著可編程布線資源。通過它們實現CLB與CLB之間、CLB與IOB之間以及全局時鐘等信號與CLB和IOB之間的連接。

在Xilinx公司的高性能產品中,已將乘法器、數字信號處理器等集成在FPGA中,大大增強了FPGA的功能。同時,為了使芯片穩定可靠地工作,其內部都設有數字時鐘管理模塊。由于這些內容已超出本書討論范圍,所以此處只介紹FPGA中幾個最基本的功能模塊。

可編程邏輯模塊CLB,CLB是FPGA中的基本邏輯模塊,它可實現絕大多數的邏輯功能,其簡化的原理框圖如圖7.4.5所示。構成CLB的基礎是邏輯單元(LC②),一個LC中包括一個4輸人LUT、進位及控制邏輯和一個D觸發器(EC為時鐘使能控制端)。每個CLB包含4個LC,并將每2個LC組織在1個微片(slice)中,圖中可見有2個微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4個微片,即含有8個LC。CLB的輸入來自可編程布線區,其輸出再回送到內部布線區。

圖7.4.5 Spartan-Ⅱ、Ⅴirtex系列簡化的CLB原理框圖

實際上,「PGA采用多層布局布線結構,并非只能在模塊間的空隙處布線。

Logic Cell的縮寫,存儲器、復雜可編程器件和明場可編程門陣列.

來自CLB以外布線區的4個輸入變量同時送人F1~F4和相應的C1~C4,第5個輸入變量送至BX端。F-LUT、G-LUT的輸出和BX經數據選擇器F5擴展為5變量邏輯函數。該結果可直接由F5端輸出,也可經XMUX、DXMUX和D觸發器,由X和/或X0端輸出。

實現6變量任意邏輯函數,實現6變量任意邏輯函數需用2個微片。在實現5變量函數基礎上,將另一個微片的乃的輸出送入此微片的F5JⅣ輸人端,第6個變量送人By端。數據選擇器F5的輸出、F5JⅣ和By經數據選擇器F6擴展為6變量邏輯函數。該結果經YMUX、DYMUX和D觸發器,由y和/或yQ端輸出。

2位二進制加法器,由于加法運算涉及進位問題,所以CLB中專門設計了進位鏈,一個微片可以完成2位二進制數的加法運算。實現加法運算時,加數A1A。和被加數B1BO分別送入G2F2和G1F1,即C2=A1,Cl=B1,F2=A0,F1=BO。通過編程使兩個LUT分別實現F2①F1和C2①C1,同時編程使XMUx和YMUX選通異或門的輸出,使xCMUX和YCMUX選通與門的輸出,使YBMUX選通上端CY的輸出。這樣,圖7.4,6可以簡化為圖7.4.7的形式。其中,低位的和So=A0①BO①Ci,進位Co為Co=(Ao①Bo)AOBO+(Ao①BO)C~1=(AOBo+AOBO)AOBO+(Ao①Bo)C~1=AoBO+(Ao∈)Bo)C~1

高位的和及進位有相同的結果,由此看出,電路上、下兩部分分別為兩個全加器。

圖7.4.6所示電路中的與門、ⅩCMUX、YCMUX、C~1^MUX和CY構成進位邏輯電路,也稱進位鏈,可以與其他微片串聯實現更多位的加法運算。當此微片為最低位時,通過編程使C~1MUX選通BX,且使Bx二0。

時序邏輯的實現,圖7.4.6中觸發器的輸出,經布線區反饋給輸人,再經LUT產生激勵函數驅動觸發器的D端,從而構成時序邏輯電路。觸發器的激勵函數也可通過DXMUX(DYMUX)直接取自BX(By)。由多個CLB便可構成復雜的時序邏輯電路。

由于LUT就是一個16×1位的SRAM,所以CLB也可用來作存儲器使用,不過此時LUT中的內容不再是預先配置好的,而是在正常工作時可以隨時讀寫的,而且LUT不能再作為邏輯函數產生器使用。LUT也可以被設置成16位移位寄存器使用。另外,為彌補LUT構成RAM在容量上的不足,在FPGA中還增加了RAM塊。這些RAM塊以列的形式排列,在Spartan-Ⅱ系列中有兩存儲器、復雜可編程器件利現場可編程閘陣.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607