PCA9600DP 限流電阻繼電器

發布時間:2020/2/9 22:20:56 訪問次數:949

由上述可知,TTL驅動74HCT系列CMOs時,不需另加接口電路。因此,在數字電路設計中,也常用74HCT系列器件當作接口電路,以省去上拉電阻。

低電壓CMOS電路及接口,CMOs電路的動態功耗為PD=(CPD+CL)吒/,為減小功耗,采用低電源電壓。另外,半導體制造工藝使晶體管尺寸越做越小,CMOs的柵極與源極、柵極與漏極間的絕緣層也越來越薄,不足以承受5V電源電壓,半導體廠家推出了供電電壓分別為3.3V、2.5V和1.8V等一系列低電壓集成電路。為了降低成本,能夠與原有外圍設各兼容,在同一系統中采用不同供電電壓的邏輯器件,為此,需要考慮不同邏輯器件之間的接口問題。

3.3Ⅴ供電電源的CMOs邏輯器件74LⅤC系列具有5V輸入容限,即輸入端可以承受5Ⅴ輸入電壓,因此,可以 與HCT系列CMOs或TTL系列直接接 (⒉5v,3.3V),uc2(3,3V/5V)口。當用74LVC系列驅動HC系列CMOS門時,高電平參數不滿足式(3.6.3),可以用上拉電阻、OD門或采用專門的邏輯電平轉換器。

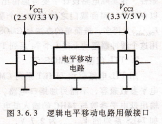

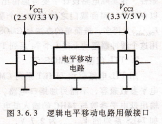

平移動電路用做接口,74ALVC1m2ZI5可用于不同CMOS系列或mL系列之間的邏輯電平轉移,它采用兩種直流電源uc1和uc2,如圖3.6.3所示。

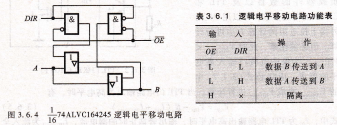

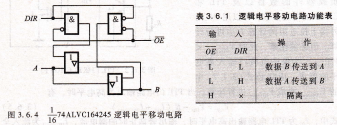

74ALVC1245的結構與功能表分別如圖3.6.4和表3.6.1所示,它是雙向傳輸器件,可以接收2.5V(或3.3V)供電電壓的邏輯電平,輸出3.3V(或5V)供電電壓的邏輯電平。反之,它也可以接收3.3Ⅴ3.3V)供電電壓的邏輯電平。

表3.6.1 邏輯電平移動電路,功能表邏輯門電路0E輸操作圖3.6.4,74ALvC164245邏輯電平移動電路,電平移動電路.

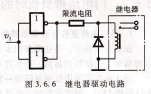

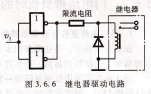

如果負載所需的電流不特別大,例如微型繼電器,可以將兩個反相器并聯作為驅動電路,如圖3.6.6所示。即使封裝在同一芯片內的兩個反相器的參數也有差別,因此,并聯后總的最大負載電流略v1小于單個門最大負載電流的兩倍。

如果負載所需的電流比較大,達到幾百毫安,則需要在數字電路的輸出端與負 圖3.6.6繼電器驅動電路載之間接入一個功率驅動器件,稱之為外圍驅動器件。它的輸入與數字集成電路(例如CMOS、TTL和ECL等)兼容,輸出端可直接用于驅動機電系統。

外圍驅動器件(例如達林頓晶體管陣列ULN2003 A等)的電路形式與結構一般都具有以下兩個特點:一是采用集電極開路輸出結構,其輸出高電平凡乎等于外加電壓,通過調節外加電壓來滿足不同負載對高電平電壓的要求。二是驅動器電路的輸出晶體管具有較強的帶負載能力,能提供較大的電流。具體外圍驅動器的電路結構可查閱有關數據手冊。

利用邏輯門電路(CMOs或TTL)做具體的電路設計時,還應當注意下列幾個實際問題:

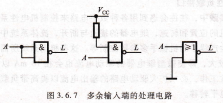

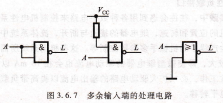

多余輸入端的處理措施,集成邏輯門電路在使用時,一般不讓多余的輸入端懸空,以防止干擾信號引人。對多余輸入端的處理以不改變電路工作狀態及穩定可靠為原則,如圖3.6.7所示。一是將它與其他輸入端并接在一起。二是根據邏輯要求,與門或者與非門的多余輸入端通過1~3kΩ電阻接正電源,對CMOs電路可以直接接電源。或門或者或非門的多余輸入端接地。對于高速電路的設計,并接會增加輸入端等效電容性負載,而使信號的傳輸速度下降,最好采用圖3.6.7所示的后兩種方法。

限流電阻繼電器,圖3.6.7 多余輸人端的處理電路

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

由上述可知,TTL驅動74HCT系列CMOs時,不需另加接口電路。因此,在數字電路設計中,也常用74HCT系列器件當作接口電路,以省去上拉電阻。

低電壓CMOS電路及接口,CMOs電路的動態功耗為PD=(CPD+CL)吒/,為減小功耗,采用低電源電壓。另外,半導體制造工藝使晶體管尺寸越做越小,CMOs的柵極與源極、柵極與漏極間的絕緣層也越來越薄,不足以承受5V電源電壓,半導體廠家推出了供電電壓分別為3.3V、2.5V和1.8V等一系列低電壓集成電路。為了降低成本,能夠與原有外圍設各兼容,在同一系統中采用不同供電電壓的邏輯器件,為此,需要考慮不同邏輯器件之間的接口問題。

3.3Ⅴ供電電源的CMOs邏輯器件74LⅤC系列具有5V輸入容限,即輸入端可以承受5Ⅴ輸入電壓,因此,可以 與HCT系列CMOs或TTL系列直接接 (⒉5v,3.3V),uc2(3,3V/5V)口。當用74LVC系列驅動HC系列CMOS門時,高電平參數不滿足式(3.6.3),可以用上拉電阻、OD門或采用專門的邏輯電平轉換器。

平移動電路用做接口,74ALVC1m2ZI5可用于不同CMOS系列或mL系列之間的邏輯電平轉移,它采用兩種直流電源uc1和uc2,如圖3.6.3所示。

74ALVC1245的結構與功能表分別如圖3.6.4和表3.6.1所示,它是雙向傳輸器件,可以接收2.5V(或3.3V)供電電壓的邏輯電平,輸出3.3V(或5V)供電電壓的邏輯電平。反之,它也可以接收3.3Ⅴ3.3V)供電電壓的邏輯電平。

表3.6.1 邏輯電平移動電路,功能表邏輯門電路0E輸操作圖3.6.4,74ALvC164245邏輯電平移動電路,電平移動電路.

如果負載所需的電流不特別大,例如微型繼電器,可以將兩個反相器并聯作為驅動電路,如圖3.6.6所示。即使封裝在同一芯片內的兩個反相器的參數也有差別,因此,并聯后總的最大負載電流略v1小于單個門最大負載電流的兩倍。

如果負載所需的電流比較大,達到幾百毫安,則需要在數字電路的輸出端與負 圖3.6.6繼電器驅動電路載之間接入一個功率驅動器件,稱之為外圍驅動器件。它的輸入與數字集成電路(例如CMOS、TTL和ECL等)兼容,輸出端可直接用于驅動機電系統。

外圍驅動器件(例如達林頓晶體管陣列ULN2003 A等)的電路形式與結構一般都具有以下兩個特點:一是采用集電極開路輸出結構,其輸出高電平凡乎等于外加電壓,通過調節外加電壓來滿足不同負載對高電平電壓的要求。二是驅動器電路的輸出晶體管具有較強的帶負載能力,能提供較大的電流。具體外圍驅動器的電路結構可查閱有關數據手冊。

利用邏輯門電路(CMOs或TTL)做具體的電路設計時,還應當注意下列幾個實際問題:

多余輸入端的處理措施,集成邏輯門電路在使用時,一般不讓多余的輸入端懸空,以防止干擾信號引人。對多余輸入端的處理以不改變電路工作狀態及穩定可靠為原則,如圖3.6.7所示。一是將它與其他輸入端并接在一起。二是根據邏輯要求,與門或者與非門的多余輸入端通過1~3kΩ電阻接正電源,對CMOs電路可以直接接電源。或門或者或非門的多余輸入端接地。對于高速電路的設計,并接會增加輸入端等效電容性負載,而使信號的傳輸速度下降,最好采用圖3.6.7所示的后兩種方法。

限流電阻繼電器,圖3.6.7 多余輸人端的處理電路

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607