Z86E2101ZDF 邏輯電路的功能及基本應用

發布時間:2020/2/10 12:22:08 訪問次數:1201

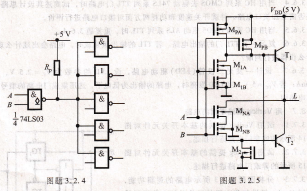

3.24 圖題3,2.4所不為集電極開路門74LS03驅動5個CMOS邏輯門,已知0C門輸出管截止時的漏電流v7=0.2 mA;負載門的參數為:ym(mml=4Ⅴ,ylLt mdx)=1v9JIL=rm=1uA。試計算上打電阻的值。

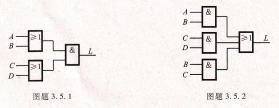

3.2.5 圖題32,5表示一2輸人端BiCMOs與非門電路,試分析該電路是怎樣實現與非邏輯關系(即L=1・B)的。

路的抗實現門電路uL(max)=u1・630VoH(min)=0.980

3.4 砷化鎵邏輯門電路

3.41 試計算3.4節介紹的兩種砷干擾能力強。

3,5 邏輯描述中的幾個問題

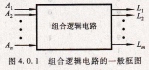

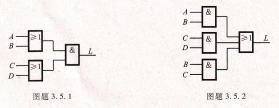

3.5,1 試對圖題3.5,1所示電路的

3.5,2 電路如圖題3.5.2所示,試

圖題3.5,1試計算它的噪聲容限。

化鎵邏輯門電路的噪聲容限,并判斷哪種電邏輯門進行變換,使其可以用單一的或非門用與非門實現。

圖題3,5,2 數字系統中常用的各種數字部件,就其結構和工作原理而言可分為兩大類,即組合邏輯電路和時序邏輯電路。本章首先介紹組合邏輯電路的定義、分析和設計,并闡述菀爭冒險產生的原因及消除方法。然后討論典型的中規模集成組合邏輯電路的功能及基本應用,它們包括編碼器和譯碼器、數據選

擇器和數據分配器、數值比較器、算術/邏輯運算單元等。最后介紹組合邏輯電路的Verilog HDL描述以及用可編程邏輯器件PLD的實現方法。

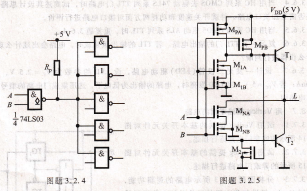

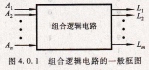

對于一個邏輯電路,其輸出狀態在任何時刻只取決于同一時刻的輸入狀態,而與電路原來的狀態無關,這種電路被定義為組合邏輯電路。組合邏輯電路的一般框圖如圖4.0.1所示,其輸出與輸入之間的邏輯關系可用如下的邏輯函數來描述,即u=r(Al,A2,..,a3) (J=1,2,…,7n) (4.0.1)

式中找,A2,・・・,An一輸入變量。

組合邏輯電路的結構具有,如下的特點:輸出、輸入之間沒有反饋延遲通路;電路中不含具有記憶功能的元件。

圖4,0.1 組合邏輯電路的一般框圖,組合邏輯電路

3.24 圖題3,2.4所不為集電極開路門74LS03驅動5個CMOS邏輯門,已知0C門輸出管截止時的漏電流v7=0.2 mA;負載門的參數為:ym(mml=4Ⅴ,ylLt mdx)=1v9JIL=rm=1uA。試計算上打電阻的值。

3.2.5 圖題32,5表示一2輸人端BiCMOs與非門電路,試分析該電路是怎樣實現與非邏輯關系(即L=1・B)的。

路的抗實現門電路uL(max)=u1・630VoH(min)=0.980

3.4 砷化鎵邏輯門電路

3.41 試計算3.4節介紹的兩種砷干擾能力強。

3,5 邏輯描述中的幾個問題

3.5,1 試對圖題3.5,1所示電路的

3.5,2 電路如圖題3.5.2所示,試

圖題3.5,1試計算它的噪聲容限。

化鎵邏輯門電路的噪聲容限,并判斷哪種電邏輯門進行變換,使其可以用單一的或非門用與非門實現。

圖題3,5,2 數字系統中常用的各種數字部件,就其結構和工作原理而言可分為兩大類,即組合邏輯電路和時序邏輯電路。本章首先介紹組合邏輯電路的定義、分析和設計,并闡述菀爭冒險產生的原因及消除方法。然后討論典型的中規模集成組合邏輯電路的功能及基本應用,它們包括編碼器和譯碼器、數據選

擇器和數據分配器、數值比較器、算術/邏輯運算單元等。最后介紹組合邏輯電路的Verilog HDL描述以及用可編程邏輯器件PLD的實現方法。

對于一個邏輯電路,其輸出狀態在任何時刻只取決于同一時刻的輸入狀態,而與電路原來的狀態無關,這種電路被定義為組合邏輯電路。組合邏輯電路的一般框圖如圖4.0.1所示,其輸出與輸入之間的邏輯關系可用如下的邏輯函數來描述,即u=r(Al,A2,..,a3) (J=1,2,…,7n) (4.0.1)

式中找,A2,・・・,An一輸入變量。

組合邏輯電路的結構具有,如下的特點:輸出、輸入之間沒有反饋延遲通路;電路中不含具有記憶功能的元件。

圖4,0.1 組合邏輯電路的一般框圖,組合邏輯電路

公網安備44030402000607

公網安備44030402000607