HD81806RP 高電平輸出時的漏電流

發布時間:2020/2/9 22:52:02 訪問次數:1590

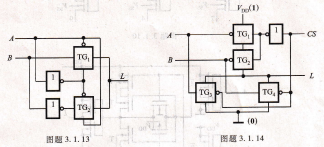

HD81806RP3.1.13 邏輯電路。

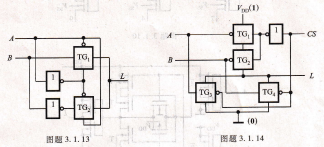

3.1.14 電路的邏輯功能。

試分析圖題3.1.13所示傳輸門構其邏輯表達式,說明它是什出其真值表,說明該電路的TTL邏輯門電路,輸人端接10 kΩ的電阻到地。

3.2.3 設有74LS04反本目器驅動T兩個74ALS04反本目器,邏輯門電路使用中的幾個實際問題

3.6.1 當CMOs和TTL兩種門電路相互連接時,要考慮哪幾個電壓和電流參數?這些參數應滿足怎樣的關系?

3,6.2 當用74LS系列TTL電路去驅動74HC系列CMOs電路時,試簡述其設計思路,是否需要接口電路?計算其扇出數,并對接口電路就開關速度和功耗兩方面做出評價(設用一個74LS邏輯門作為驅動器件,并且它的高電平輸出時的漏電流為0.2 mA)。

3,6.3 當用74ALS系列TTL去驅動74HC系列CMOS時,重復題3.6.2。

3,7.3 分析圖題3.7.3所示電路的邏輯功能,并使用Verilog提供的基本開關元件對該電路進行描下層

3.6 邏輯門電路使用中的幾個實際問題

3.6.1 當CMOs和TTL兩種門電路相互連接時,要考慮哪幾個電壓和電流參數?這些參數應滿足怎樣的關系?

3,6.2 當用74LS系列TTL電路去驅動74HC系列CMOs電路時,試簡述其設計思路,是否需要接口電路?計算其扇出數,并對接口電路就開關速度和功耗兩方面做出評價(設用一個74LS邏輯門作為驅動器件,并且它的高電平輸出時的漏電流為0.2 mA)。

3,6.3 當用74ALS系列TTL去驅動74HC系列CMOS時,重復題3.6.2。

3.7.3 分析圖題3.7.3所示電路的邏輯功能,并使用Verilog提供的基本開關元件對該電路進行描下層.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

HD81806RP3.1.13 邏輯電路。

3.1.14 電路的邏輯功能。

試分析圖題3.1.13所示傳輸門構其邏輯表達式,說明它是什出其真值表,說明該電路的TTL邏輯門電路,輸人端接10 kΩ的電阻到地。

3.2.3 設有74LS04反本目器驅動T兩個74ALS04反本目器,邏輯門電路使用中的幾個實際問題

3.6.1 當CMOs和TTL兩種門電路相互連接時,要考慮哪幾個電壓和電流參數?這些參數應滿足怎樣的關系?

3,6.2 當用74LS系列TTL電路去驅動74HC系列CMOs電路時,試簡述其設計思路,是否需要接口電路?計算其扇出數,并對接口電路就開關速度和功耗兩方面做出評價(設用一個74LS邏輯門作為驅動器件,并且它的高電平輸出時的漏電流為0.2 mA)。

3,6.3 當用74ALS系列TTL去驅動74HC系列CMOS時,重復題3.6.2。

3,7.3 分析圖題3.7.3所示電路的邏輯功能,并使用Verilog提供的基本開關元件對該電路進行描下層

3.6 邏輯門電路使用中的幾個實際問題

3.6.1 當CMOs和TTL兩種門電路相互連接時,要考慮哪幾個電壓和電流參數?這些參數應滿足怎樣的關系?

3,6.2 當用74LS系列TTL電路去驅動74HC系列CMOs電路時,試簡述其設計思路,是否需要接口電路?計算其扇出數,并對接口電路就開關速度和功耗兩方面做出評價(設用一個74LS邏輯門作為驅動器件,并且它的高電平輸出時的漏電流為0.2 mA)。

3,6.3 當用74ALS系列TTL去驅動74HC系列CMOS時,重復題3.6.2。

3.7.3 分析圖題3.7.3所示電路的邏輯功能,并使用Verilog提供的基本開關元件對該電路進行描下層.

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607