LEMC3225T2R2M 影響開關速度的主要因素

發布時間:2020/2/9 22:43:53 訪問次數:1347

pmos(L,Vdd,A);

pmos(L,Vdd,B);

nmos(L,W1,B);

nmos(W1,GND,A);

endnnodule

//將兩個NMOs管之間的連接點定義為W1

//PMOS管的源極與Ⅴdd相連

//兩個PMOs管并行連接

//兩個NMOS管串行連接

//NMOS管的源極與地相連

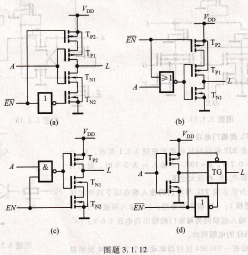

CMOs傳輸門電路的Verilog建模,Verilog語言中用關鍵詞cm。s定義了基本傳輸門元件模型,它有一個輸出端、一個輸人端和兩個控制端,如圖3.1.11所示,習慣上也稱之為cmOs開關。

其用法如下:

cmos c1(輸出信號,輸人信號,TN管控制信號,TP管控制信號);

通常TN管控制信號和TP管控制信號彼此是互補的,當TN管控制信號為1,Tp管控制信號為0時,CMOs開關導通;如果TN管控制信號為0,TP管控制信號為1時,CMOs開關的輸出呈現出高阻抗值z。CMOs開關的電源和地通常與MOS管的襯底相連,故調用cmos元件時,不需要考慮電源與地的連接問題。調用名c1可以省略。

關鍵詞rcmos定義了傳輸門元件另一種模型,字母r說明傳輸門元件的輸人端和輸出端之間存在著電阻,當信號通過時會造成幅度衰減。注意,Verilog語言中定義的兩種傳輸門元件信號是單向傳輸的,與前面介紹的實際傳輸門元件存在一定差異。

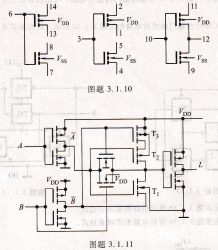

圖3.1.12所示電路的Verilog模型如例3.1.12所示。程序中調用了一個在開關級自定義的下層模塊inverter,其調用名為v1(注意,調用下層模塊時,調用名不能省略),完成反相的功能。還調用了兩個cmos開關元件,它們是Ver止og內置的基本元件,故調用名被省略。

例3.1,12

//2-to-1 1multiplexer with CMOs switchs Fig.3.1.27

mlodule mymux2to1(X,Y,C,L);

input X, Y, c;

output L;

wire Cnot;

///instantiate inverter

invener v1(Cn。t,C);

//instantiate clrlos switch

c1mos(L,X,Cn。t,C);//(output,input,ncontrol,pcontro1)

cmos(L,Y,C,Cnot);

endmodule

//CMOs inverter Fig.3.1.8

module inverter(Vo,Ⅴi);

input Vi;

output Vo;

supply1Vdd;

supplyO GND;

pmos(Ⅴo,Vdd,Ⅴi); //(漏極,源極,控制柵極)

nm.os(Ⅴo,GND,Vi);

endnnodule

邏輯門電路的主要技術參數有輸入和輸出高、低電平的最大值或最小值,噪聲容限,傳輸延遲時間,功耗,延遲一功耗積,扇入數和扇出數等。

在數字電路中,不論哪一種邏輯門電路,其中的關鍵器件是MOS管或BJT。它們均可以作為開關器件。影響它們開關速度的主要因素是器件內部各電極之間的結電容。

CMOs邏輯門電路是目前應用最廣泛的邏輯門電路。其優點是集成度高,功耗低,扇出數大(指帶同類門負載),噪聲容限亦大,開關速度較高。CMOs邏輯門電路中,為了實現線與的邏輯功能,可以采用漏極開路門和三態門.

NMOs邏輯門電路結構簡單,易于集成化,曾在大規模集成電路中應用較多。

TTL邏輯門電路是應用較廣泛的門電路之一,電路由若干BJT和電阻組成。TTL反相器的輸入級由BJT構成,輸出級采用推拉式結構,其目的是為提高開關速度和增強帶負載的能力。

t~1 BiCMOS是取MOS和TTL兩者的優勢,其開關速度較高,功耗亦較低。

利用肖特基二極管構成抗飽和TTL電路,可以提高開關速度。已ECL邏輯門電路是以差分放大電路為基礎的,它不工作在BJT的飽和區,因而開關速度較高。其缺點是功耗較大,噪聲容限低。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

pmos(L,Vdd,A);

pmos(L,Vdd,B);

nmos(L,W1,B);

nmos(W1,GND,A);

endnnodule

//將兩個NMOs管之間的連接點定義為W1

//PMOS管的源極與Ⅴdd相連

//兩個PMOs管并行連接

//兩個NMOS管串行連接

//NMOS管的源極與地相連

CMOs傳輸門電路的Verilog建模,Verilog語言中用關鍵詞cm。s定義了基本傳輸門元件模型,它有一個輸出端、一個輸人端和兩個控制端,如圖3.1.11所示,習慣上也稱之為cmOs開關。

其用法如下:

cmos c1(輸出信號,輸人信號,TN管控制信號,TP管控制信號);

通常TN管控制信號和TP管控制信號彼此是互補的,當TN管控制信號為1,Tp管控制信號為0時,CMOs開關導通;如果TN管控制信號為0,TP管控制信號為1時,CMOs開關的輸出呈現出高阻抗值z。CMOs開關的電源和地通常與MOS管的襯底相連,故調用cmos元件時,不需要考慮電源與地的連接問題。調用名c1可以省略。

關鍵詞rcmos定義了傳輸門元件另一種模型,字母r說明傳輸門元件的輸人端和輸出端之間存在著電阻,當信號通過時會造成幅度衰減。注意,Verilog語言中定義的兩種傳輸門元件信號是單向傳輸的,與前面介紹的實際傳輸門元件存在一定差異。

圖3.1.12所示電路的Verilog模型如例3.1.12所示。程序中調用了一個在開關級自定義的下層模塊inverter,其調用名為v1(注意,調用下層模塊時,調用名不能省略),完成反相的功能。還調用了兩個cmos開關元件,它們是Ver止og內置的基本元件,故調用名被省略。

例3.1,12

//2-to-1 1multiplexer with CMOs switchs Fig.3.1.27

mlodule mymux2to1(X,Y,C,L);

input X, Y, c;

output L;

wire Cnot;

///instantiate inverter

invener v1(Cn。t,C);

//instantiate clrlos switch

c1mos(L,X,Cn。t,C);//(output,input,ncontrol,pcontro1)

cmos(L,Y,C,Cnot);

endmodule

//CMOs inverter Fig.3.1.8

module inverter(Vo,Ⅴi);

input Vi;

output Vo;

supply1Vdd;

supplyO GND;

pmos(Ⅴo,Vdd,Ⅴi); //(漏極,源極,控制柵極)

nm.os(Ⅴo,GND,Vi);

endnnodule

邏輯門電路的主要技術參數有輸入和輸出高、低電平的最大值或最小值,噪聲容限,傳輸延遲時間,功耗,延遲一功耗積,扇入數和扇出數等。

在數字電路中,不論哪一種邏輯門電路,其中的關鍵器件是MOS管或BJT。它們均可以作為開關器件。影響它們開關速度的主要因素是器件內部各電極之間的結電容。

CMOs邏輯門電路是目前應用最廣泛的邏輯門電路。其優點是集成度高,功耗低,扇出數大(指帶同類門負載),噪聲容限亦大,開關速度較高。CMOs邏輯門電路中,為了實現線與的邏輯功能,可以采用漏極開路門和三態門.

NMOs邏輯門電路結構簡單,易于集成化,曾在大規模集成電路中應用較多。

TTL邏輯門電路是應用較廣泛的門電路之一,電路由若干BJT和電阻組成。TTL反相器的輸入級由BJT構成,輸出級采用推拉式結構,其目的是為提高開關速度和增強帶負載的能力。

t~1 BiCMOS是取MOS和TTL兩者的優勢,其開關速度較高,功耗亦較低。

利用肖特基二極管構成抗飽和TTL電路,可以提高開關速度。已ECL邏輯門電路是以差分放大電路為基礎的,它不工作在BJT的飽和區,因而開關速度較高。其缺點是功耗較大,噪聲容限低。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607