MI-22M-IW PMOS開關的輸出呈現高阻值z

發布時間:2020/2/9 22:35:18 訪問次數:1836

MI-22M-IW這是Verilog語言提供的最低層次的描述。由于Quartus Ⅱ軟件不支持Ver~ilog語言內置的開關級元件,所以本節介紹的開關級電路模型需用其他的通用仿真器(例如Modelsim、Active HDL、Ⅴerilog XL等)仿真。

CMOs r1電路的Verrog建模,為了對數字開關邏輯電路建模,Ⅴerilog提供了十多個內置的基本開關元件。關鍵詞nmos、pmos分別定義了最基本的NMOs管和PMOs管模型,調用時按照下列格式說明它的三個端口信號。

mmos n1(漏極,源極,控制柵極);調用nmos開關元件

pmos p1(漏極,源極,控制柵極);調用pmos開關元件

對NMOs元件,如果控制柵極信號為1,則NMOs開關導通,信號能夠從管子的源極傳輸到漏極,如果控制柵極信號為0,則輸出呈現高阻值z。類似地,如果控制柵極信號為0時,PMOS開關導通,否則,PMOs開關的輸出呈現高阻值z。由于nmos、pmos是基本元件,故調用名n1、p1可以省略。

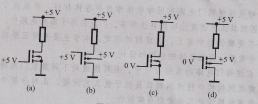

關鍵詞rnmos、rpmos分別是NMOs管和PMOs管另一種模型,前面的字母r說明MOs管的輸入端和輸出端之間存在著電阻,當信號從MOS管的輸人傳輸至輸出時,信號的幅度會衰減,它們的用法與nmos、pmos元件相同,如圖3.1.4。

Ⅴerilog語言中用關鍵詞supply1、supply0分別定義了電源線和地線。supˉply1與電路圖中的yDD等效,在整個仿真期間將線網置邏輯1;supplyO與電路圖中的地線或yss等效,在整個仿真期間將線網置邏輯0。它們的用法如下:

supply1 Ⅴdd;

supplyO GND;

兩輸人CMOs與非門電路的描述如例3.7.1所示。兩個PMOs管并聯,且源極都與電源Vdd連接,漏極都與輸出L相連,兩個管子的柵極分別與輸入A、B相連;兩個NMOs管串聯,有一個公共節點W1,第一個NMOs管的漏極與輸出L相連,第二個NMOS管的源極與地線GND相連,兩個NMOS管的柵極分別與輸人A、B相連。

3.1.5 為什么說74HC系列CMOs與非門在+5V電源工作時,輸人端在以下四種接法下都屬于邏輯0:(1)輸人端接地;(2)輸人端接低于15V的電源;(3)輸人端接同類與非門的輸出低電壓0.1V;(4)輸人端接10 kΩ的電阻到地。

3.1.7 求圖題3.1.7所示電路的輸出邏輯表達式。

3.1.8 用三個漏極開路與非門74HC03和一個TTL與非門74 LS00實現圖題3.1.7所不的電路,已知CMOs管截止時的漏電流f。z=5uA,試計算RP(miⅡ和RPrnux)。

3.1.9 圖題3.1.9表示三態門作總線傳輸的示意圖,圖中刀個二態門的輸出接到數據傳輸總線,DI、D2、…、D`t為數據輸人端,CsI、Cs2、・・・、Cs″為片選信號輸人端。試問:(1)Cs信號如何進行控制,以便數據DI、D2、…、D″通過該總線進行正常傳輸;(2)Cs信號能否有兩個或兩個以上同時有效9如果Cs出現兩個或兩個以上有效,可能發生什么情況?(3)如果所有Cs信號均無效,總線處在什么狀態?

3.1.10 CMOS集成芯片4007中包含兩個互補對和一個反相器,其引出端如圖題3.1.10所示,試分別連接:(1)三個反相器;(2)3輸人端或非門;(3)3輸人端與非門;

(4)或與非門[z=C(△+B)];(5)傳輸門(一個非門控制兩個傳輸門分時傳送)。

3.1.11 試分析圖題3.1.11所示某CMOs器件的電路,寫出其邏輯表達式,說明它是什么邏輯電路。

3.1.12 試分析圖題3.1.12所示的CMOs電路,說明它們的邏輯功能。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

MI-22M-IW這是Verilog語言提供的最低層次的描述。由于Quartus Ⅱ軟件不支持Ver~ilog語言內置的開關級元件,所以本節介紹的開關級電路模型需用其他的通用仿真器(例如Modelsim、Active HDL、Ⅴerilog XL等)仿真。

CMOs r1電路的Verrog建模,為了對數字開關邏輯電路建模,Ⅴerilog提供了十多個內置的基本開關元件。關鍵詞nmos、pmos分別定義了最基本的NMOs管和PMOs管模型,調用時按照下列格式說明它的三個端口信號。

mmos n1(漏極,源極,控制柵極);調用nmos開關元件

pmos p1(漏極,源極,控制柵極);調用pmos開關元件

對NMOs元件,如果控制柵極信號為1,則NMOs開關導通,信號能夠從管子的源極傳輸到漏極,如果控制柵極信號為0,則輸出呈現高阻值z。類似地,如果控制柵極信號為0時,PMOS開關導通,否則,PMOs開關的輸出呈現高阻值z。由于nmos、pmos是基本元件,故調用名n1、p1可以省略。

關鍵詞rnmos、rpmos分別是NMOs管和PMOs管另一種模型,前面的字母r說明MOs管的輸入端和輸出端之間存在著電阻,當信號從MOS管的輸人傳輸至輸出時,信號的幅度會衰減,它們的用法與nmos、pmos元件相同,如圖3.1.4。

Ⅴerilog語言中用關鍵詞supply1、supply0分別定義了電源線和地線。supˉply1與電路圖中的yDD等效,在整個仿真期間將線網置邏輯1;supplyO與電路圖中的地線或yss等效,在整個仿真期間將線網置邏輯0。它們的用法如下:

supply1 Ⅴdd;

supplyO GND;

兩輸人CMOs與非門電路的描述如例3.7.1所示。兩個PMOs管并聯,且源極都與電源Vdd連接,漏極都與輸出L相連,兩個管子的柵極分別與輸入A、B相連;兩個NMOs管串聯,有一個公共節點W1,第一個NMOs管的漏極與輸出L相連,第二個NMOS管的源極與地線GND相連,兩個NMOS管的柵極分別與輸人A、B相連。

3.1.5 為什么說74HC系列CMOs與非門在+5V電源工作時,輸人端在以下四種接法下都屬于邏輯0:(1)輸人端接地;(2)輸人端接低于15V的電源;(3)輸人端接同類與非門的輸出低電壓0.1V;(4)輸人端接10 kΩ的電阻到地。

3.1.7 求圖題3.1.7所示電路的輸出邏輯表達式。

3.1.8 用三個漏極開路與非門74HC03和一個TTL與非門74 LS00實現圖題3.1.7所不的電路,已知CMOs管截止時的漏電流f。z=5uA,試計算RP(miⅡ和RPrnux)。

3.1.9 圖題3.1.9表示三態門作總線傳輸的示意圖,圖中刀個二態門的輸出接到數據傳輸總線,DI、D2、…、D`t為數據輸人端,CsI、Cs2、・・・、Cs″為片選信號輸人端。試問:(1)Cs信號如何進行控制,以便數據DI、D2、…、D″通過該總線進行正常傳輸;(2)Cs信號能否有兩個或兩個以上同時有效9如果Cs出現兩個或兩個以上有效,可能發生什么情況?(3)如果所有Cs信號均無效,總線處在什么狀態?

3.1.10 CMOS集成芯片4007中包含兩個互補對和一個反相器,其引出端如圖題3.1.10所示,試分別連接:(1)三個反相器;(2)3輸人端或非門;(3)3輸人端與非門;

(4)或與非門[z=C(△+B)];(5)傳輸門(一個非門控制兩個傳輸門分時傳送)。

3.1.11 試分析圖題3.1.11所示某CMOs器件的電路,寫出其邏輯表達式,說明它是什么邏輯電路。

3.1.12 試分析圖題3.1.12所示的CMOs電路,說明它們的邏輯功能。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607