LTC6903CMS8TR 數據選擇器的好處是無的轉動

發布時間:2020/2/10 19:20:14 訪問次數:1608

LTC6903CMS8TR邏輯函數產生器,根據8選1數據選擇器輸出與輸人的關系式(4.4.7)有式中mi是地址選擇輸入端s2、s1、sO構成的最小項。數據輸入作為控制信號,當DJ=1時,其對應的最小項祝g在表達式中出現,當Di=0時,對應的最小項就不出現。利用這一點將函數變換成最小項表達式,函數的變量接入地址選擇輸入端,就可以實現組合邏輯函數。

例4,4,7 試用8選1數據選擇器74HC151產生邏輯函數L=ABC+ABC+AB。

解:把所給的函數式變換成最小項表達式

L=ABC+A BC+ABC+AB C

將上式寫成如下形式

L=m3D3+5D5+m6D6+m7D7

顯然D3、D5、D6、D7都應該等于1,而式中沒有出現的最小項mO、m1、m2、m4對應的數據,輸入端D0、D1、D2、D4都應該等于0,并將使能端接低電平。由此可畫出該邏輯函數產生器的邏輯圖,如圖4.4.24所示。

通過上面例題可以看出,與使用各種邏輯門,設計組合邏輯電需對函數化簡路相比,數據選擇器的好處是無的轉動.

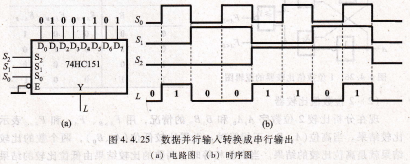

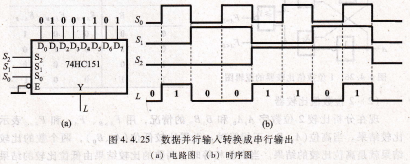

圖4.4.24 例4.4.7的邏輯圖,成的并/串行轉換的電路圖。選擇照圖中所給波形從圖4.4.25 數據并行輸入轉換成串行輸出(a)電路圖 (b)時序圖.

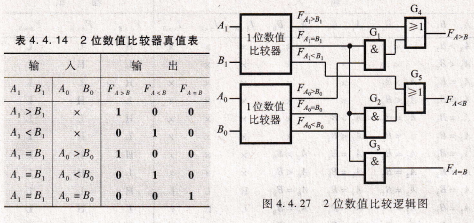

若干典型的紹合邏輯集成電路決定。利用1位數值的比較結果,可以列出簡化的真值表,如表4,4,14所示。

表4.4.14 2位數值比較器

F1>u=A1B1+(A1B1+A1B1)Bl

=F.1>1+FA1=1・FA>Bo

F1=Fa1+F.1=k・FA0<20

F4=y=F.1=1・F=0=t。

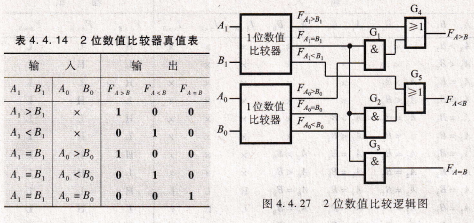

根據上式畫出邏輯圖,如圖4.4.27所示。電路利用了1位數值比較器的輸出作為中間結果。它所依據的原理是,如果2位數我A。和B1B。的高位不相等,則高位比較結果就是兩數比較結果,與低位無關。這時,高位輸出F.1=t1=0,使與門G1、G2、G3均封鎖,而或門都打開,低位比較結果不能影響或門,高位比較結果則從或門直接輸出。如果高位相等,即F=u=1,使與門G1、G2、G3均打開,同時由于F.1>1=0和FAl<k=0作用,或門也打開,低位的比較結果直接送達輸出端,即低位的比較結果決定兩數誰大、誰小或者相等。

用以上的方法可以構成更多位數值比較器。

集成數值比較器常用的中規模集成數值比較器有CMOs和TTL的產品。74x85是4位數值比較器,74x682是8位數值比較器。這里主要介紹74HC85。

集成數值比較器74HC85的功能,集成數值比較器74HC85是4位數值比較器,其功能如表4,4.15所示,輸人端包括A3~A0與B3~B。,輸出端為Fu>x、F<j、FA=£,以及擴展輸人端為r1>i、f<r和rd=g。擴展輸人端與其他數值比較器的輸出連接,以便組成位數更多的數值比較器。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

LTC6903CMS8TR邏輯函數產生器,根據8選1數據選擇器輸出與輸人的關系式(4.4.7)有式中mi是地址選擇輸入端s2、s1、sO構成的最小項。數據輸入作為控制信號,當DJ=1時,其對應的最小項祝g在表達式中出現,當Di=0時,對應的最小項就不出現。利用這一點將函數變換成最小項表達式,函數的變量接入地址選擇輸入端,就可以實現組合邏輯函數。

例4,4,7 試用8選1數據選擇器74HC151產生邏輯函數L=ABC+ABC+AB。

解:把所給的函數式變換成最小項表達式

L=ABC+A BC+ABC+AB C

將上式寫成如下形式

L=m3D3+5D5+m6D6+m7D7

顯然D3、D5、D6、D7都應該等于1,而式中沒有出現的最小項mO、m1、m2、m4對應的數據,輸入端D0、D1、D2、D4都應該等于0,并將使能端接低電平。由此可畫出該邏輯函數產生器的邏輯圖,如圖4.4.24所示。

通過上面例題可以看出,與使用各種邏輯門,設計組合邏輯電需對函數化簡路相比,數據選擇器的好處是無的轉動.

圖4.4.24 例4.4.7的邏輯圖,成的并/串行轉換的電路圖。選擇照圖中所給波形從圖4.4.25 數據并行輸入轉換成串行輸出(a)電路圖 (b)時序圖.

若干典型的紹合邏輯集成電路決定。利用1位數值的比較結果,可以列出簡化的真值表,如表4,4,14所示。

表4.4.14 2位數值比較器

F1>u=A1B1+(A1B1+A1B1)Bl

=F.1>1+FA1=1・FA>Bo

F1=Fa1+F.1=k・FA0<20

F4=y=F.1=1・F=0=t。

根據上式畫出邏輯圖,如圖4.4.27所示。電路利用了1位數值比較器的輸出作為中間結果。它所依據的原理是,如果2位數我A。和B1B。的高位不相等,則高位比較結果就是兩數比較結果,與低位無關。這時,高位輸出F.1=t1=0,使與門G1、G2、G3均封鎖,而或門都打開,低位比較結果不能影響或門,高位比較結果則從或門直接輸出。如果高位相等,即F=u=1,使與門G1、G2、G3均打開,同時由于F.1>1=0和FAl<k=0作用,或門也打開,低位的比較結果直接送達輸出端,即低位的比較結果決定兩數誰大、誰小或者相等。

用以上的方法可以構成更多位數值比較器。

集成數值比較器常用的中規模集成數值比較器有CMOs和TTL的產品。74x85是4位數值比較器,74x682是8位數值比較器。這里主要介紹74HC85。

集成數值比較器74HC85的功能,集成數值比較器74HC85是4位數值比較器,其功能如表4,4.15所示,輸人端包括A3~A0與B3~B。,輸出端為Fu>x、F<j、FA=£,以及擴展輸人端為r1>i、f<r和rd=g。擴展輸人端與其他數值比較器的輸出連接,以便組成位數更多的數值比較器。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607