CY7C291-50SC 超前進位加法器提高運算速度

發布時間:2020/2/10 19:45:12 訪問次數:2477

由式(4.4.10),并考慮多位數值相加,全加器的和數si和進位C.的邏輯表達式

s=Ao①BJ⊙Ci~1 (4.4.11)

C=A.Bi+(OB)C~1 (4.4.12)

定義兩個中間變量Cj和P。

Ci=AiB。 (4,4.13)

Pi=Aj①B. (4.4.14)

當h=j=1時,Ci=1,由式(4.4.12)得Ci=1,即產生進位,所以Ci稱為產生變量。若P=1,則我B=0,由式(4.4.12)得C=C~1,即Pi=1時,低位的進位能傳送到高位的進位輸出端,故P.稱為傳輸變量。這兩個變量都與進位信號無關。

將式(4.4.13)和式(4.4.14)代人式(4.4.11)和式(4.4.12),得

si=Pi①C~1 (4.4.15)

C=C+Pi Ci~1 (4.4.16)

由式(4.4.16)得各位進位信號的邏輯表達式如下

CO=CO+POC~1 (4.4.17a)

C1=C1+P1CO=C1+P1Co+P1POCl (4.4.17b)

C2=C2+P2C1=G2+P2G1+P2P1Co+P2P1POC~1 (4.4.17c)

C3=C3+P3C2=C3+P3G2+P3P2G1+P3P2P1C+P3P2P1PC~1 (4.4.17d)

由式(4.4.17)可知,因為進位信號只與變量Ci、P和C~1有關,而C~1是向最低位的進位信號,其值為0,所以各位的進位信號都只與兩個加數有關,它們是可以并行產生的。用與門和或門即可實現式(4.4.17)所表示的超前進位產生電路,電路圖從略。根據超前進位概念構成的集成4位加法器74HC283的結構示意圖,如圖4.4.34所示,具體邏輯圖可查閱數據手冊。

超前進位加法器大大提高了運算速度。但是,隨著加法器位數的增加,超前進位邏輯電路越來越復雜。為了解決這一矛盾,設計出了專用的超前進位產生器,用多個運算電路并行進位方式的連接,既可擴充位數又不使邏輯電路太復雜。

上面討論了4位數加法器,如果進行更多位數的加法,則需要進行擴展。例如用74HC283實現8位二進制數相加,兩片4位加法器的連接方法如圖,產生輸出端C,進位傳輸輸出端P。

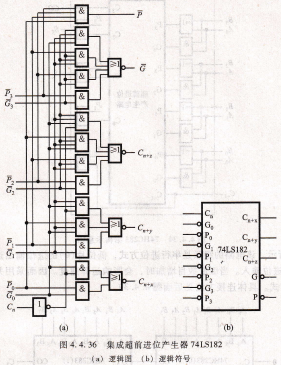

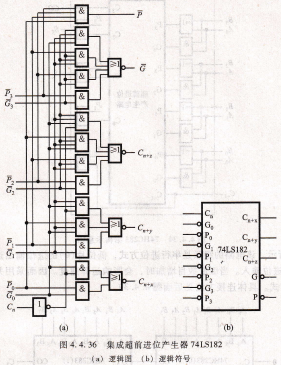

圖4.4.36 集成超(a)邏輯圖,由圖4.4.36(a)可得,前進位產生器74LS182(b)邏輯符號,為簡明起見,將上式寫為CⅡ+k=CO+PoC (4.4.18a)

同理可得

Cn+j=C1+Pl CO+P1POCn (4.4.18b)

C+z=C2+P2GI+P2P1GO+P2PlPOCn (4.4.18c)

P和G為低電平有效,所以得

P=P3P2PlPO (4.4.18d)

G=C3+P3G2+P3P2C1+P3P2Pl GO (4.4.18e)

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

由式(4.4.10),并考慮多位數值相加,全加器的和數si和進位C.的邏輯表達式

s=Ao①BJ⊙Ci~1 (4.4.11)

C=A.Bi+(OB)C~1 (4.4.12)

定義兩個中間變量Cj和P。

Ci=AiB。 (4,4.13)

Pi=Aj①B. (4.4.14)

當h=j=1時,Ci=1,由式(4.4.12)得Ci=1,即產生進位,所以Ci稱為產生變量。若P=1,則我B=0,由式(4.4.12)得C=C~1,即Pi=1時,低位的進位能傳送到高位的進位輸出端,故P.稱為傳輸變量。這兩個變量都與進位信號無關。

將式(4.4.13)和式(4.4.14)代人式(4.4.11)和式(4.4.12),得

si=Pi①C~1 (4.4.15)

C=C+Pi Ci~1 (4.4.16)

由式(4.4.16)得各位進位信號的邏輯表達式如下

CO=CO+POC~1 (4.4.17a)

C1=C1+P1CO=C1+P1Co+P1POCl (4.4.17b)

C2=C2+P2C1=G2+P2G1+P2P1Co+P2P1POC~1 (4.4.17c)

C3=C3+P3C2=C3+P3G2+P3P2G1+P3P2P1C+P3P2P1PC~1 (4.4.17d)

由式(4.4.17)可知,因為進位信號只與變量Ci、P和C~1有關,而C~1是向最低位的進位信號,其值為0,所以各位的進位信號都只與兩個加數有關,它們是可以并行產生的。用與門和或門即可實現式(4.4.17)所表示的超前進位產生電路,電路圖從略。根據超前進位概念構成的集成4位加法器74HC283的結構示意圖,如圖4.4.34所示,具體邏輯圖可查閱數據手冊。

超前進位加法器大大提高了運算速度。但是,隨著加法器位數的增加,超前進位邏輯電路越來越復雜。為了解決這一矛盾,設計出了專用的超前進位產生器,用多個運算電路并行進位方式的連接,既可擴充位數又不使邏輯電路太復雜。

上面討論了4位數加法器,如果進行更多位數的加法,則需要進行擴展。例如用74HC283實現8位二進制數相加,兩片4位加法器的連接方法如圖,產生輸出端C,進位傳輸輸出端P。

圖4.4.36 集成超(a)邏輯圖,由圖4.4.36(a)可得,前進位產生器74LS182(b)邏輯符號,為簡明起見,將上式寫為CⅡ+k=CO+PoC (4.4.18a)

同理可得

Cn+j=C1+Pl CO+P1POCn (4.4.18b)

C+z=C2+P2GI+P2P1GO+P2PlPOCn (4.4.18c)

P和G為低電平有效,所以得

P=P3P2PlPO (4.4.18d)

G=C3+P3G2+P3P2C1+P3P2Pl GO (4.4.18e)

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公網安備44030402000607

公網安備44030402000607