65納米產品CPF和統一功率格式(UPF)的RTL-to-GDSII流程

發布時間:2022/1/18 13:28:01 訪問次數:890

Talus IC實現系統已得到進一步增強,可支持通用功率格式(CPF)。通過加入CPF支持功能,Talus成為了首個可同時支持CPF和統一功率格式(UPF)的RTL-to-GDSII流程。兩種格式均允許一次性獲取規格要求并將其貫穿應用于整個流程中,可實現更好更快的低功耗集成電路(IC)實現。

通過提供兩種格式支持,微捷碼使得設計師能夠靈活地選擇最適合其設計的低功耗格式,同時還提供了各種先進的低功耗設計功能,可將功耗降至最低、最大程度提高結果質量(QoR)并減少迭代。

微捷碼的開放式架構和統一數據模型簡化了在Talus RTL-to-GDSII環境中CPF的應用。

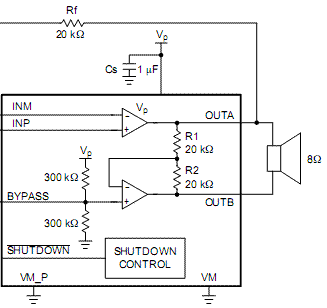

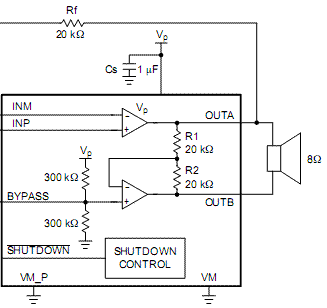

單芯片DAC和ADC中配置的數字上變頻器(DUC) DSP模塊和數字下變頻器(DDC) DSP模塊。圖2是DUC和DDC框圖示例,說明了這些數據通道常用的內部結構。這些DUC和DDC模塊有許多用途:

與數字接口的數據速率相比,內插(DUC)和抽取(DDC)轉換器的采樣速率。

轉化即將合成的DAC數據(DUC)和數字化ADC數據(DDC)的頻率。

將接口的數字數據發射導向基帶處理器(BBP)。

為每個通道實現數字增益,產生更接近系統滿量程值的碼值。

支持注入簡單的數字音調,無需數字數據鏈路,便能簡化系統快速啟動。

將每個通道的相位對齊通用基準。

65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展 35%,以幫助客戶縮短開發時間、節約開發成本。

65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展 35%,以幫助客戶縮短開發時間、節約開發成本。

每款產品均提供不同 I/O 寬度(x18 或 x36)、突發長度(B4 或 B2)和延遲(1.5、2.0 或 2.5)的多種配置標準。65 納米的 72-Mbit SRAM 采用標準的 165 引腳微間距球柵陣列 (FBGA) 封裝,為便于技術移植,其可與現有的 90納米 QDR和 DDR 器件引腳兼容。

65 納米線寬的 Quad Data Rate (QDR) 和 Double Data Rate (DDR) SRAM 器件樣品。

(素材來源:轉載自網絡,如涉版權請聯系刪除,特別感謝)

Talus IC實現系統已得到進一步增強,可支持通用功率格式(CPF)。通過加入CPF支持功能,Talus成為了首個可同時支持CPF和統一功率格式(UPF)的RTL-to-GDSII流程。兩種格式均允許一次性獲取規格要求并將其貫穿應用于整個流程中,可實現更好更快的低功耗集成電路(IC)實現。

通過提供兩種格式支持,微捷碼使得設計師能夠靈活地選擇最適合其設計的低功耗格式,同時還提供了各種先進的低功耗設計功能,可將功耗降至最低、最大程度提高結果質量(QoR)并減少迭代。

微捷碼的開放式架構和統一數據模型簡化了在Talus RTL-to-GDSII環境中CPF的應用。

單芯片DAC和ADC中配置的數字上變頻器(DUC) DSP模塊和數字下變頻器(DDC) DSP模塊。圖2是DUC和DDC框圖示例,說明了這些數據通道常用的內部結構。這些DUC和DDC模塊有許多用途:

與數字接口的數據速率相比,內插(DUC)和抽取(DDC)轉換器的采樣速率。

轉化即將合成的DAC數據(DUC)和數字化ADC數據(DDC)的頻率。

將接口的數字數據發射導向基帶處理器(BBP)。

為每個通道實現數字增益,產生更接近系統滿量程值的碼值。

支持注入簡單的數字音調,無需數字數據鏈路,便能簡化系統快速啟動。

將每個通道的相位對齊通用基準。

65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展 35%,以幫助客戶縮短開發時間、節約開發成本。

65納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展 35%,以幫助客戶縮短開發時間、節約開發成本。

每款產品均提供不同 I/O 寬度(x18 或 x36)、突發長度(B4 或 B2)和延遲(1.5、2.0 或 2.5)的多種配置標準。65 納米的 72-Mbit SRAM 采用標準的 165 引腳微間距球柵陣列 (FBGA) 封裝,為便于技術移植,其可與現有的 90納米 QDR和 DDR 器件引腳兼容。

65 納米線寬的 Quad Data Rate (QDR) 和 Double Data Rate (DDR) SRAM 器件樣品。

(素材來源:轉載自網絡,如涉版權請聯系刪除,特別感謝)

公網安備44030402000607

公網安備44030402000607