用倒裝方式替代傳統用金線去綁定內核方式縮減電流讓EMI降到最低

發布時間:2023/12/16 19:54:11 訪問次數:508

如果你把所有運算都放在SoC中運行,那就太慢了。每次模擬可能需要五到七個小時,如果你把多個模擬合并起來,就可以節省時間。

復雜ASIC中使用的同類方法現在正用于復雜的FPGA。隨著這些器件被用于功能安全類型的應用,這變得越來越重要。

這就是形式分析的用武之地,通過形式分析,可以得出錯誤的傳播路徑,然后驗證這些路徑,這些東西非常適合進行形式分析。傳統的FPGA驗證方法幾乎不可能進行這些類型的驗證。

FPGA的大小和復雜性要求其驗證過程類似于ASIC。先進的基于UVM的測試平臺支持模擬,通常也支持仿真。

從自動設計檢查到基于斷言的驗證,以及一系列強大的求解器,形式工具在這里起著關鍵的作用。盡管FPGA確實可以比ASIC更快更便宜地修改,但在大型SoC中檢測和診斷bug的難度意味著必須在進入bring-up階段之前進行徹底的驗證。

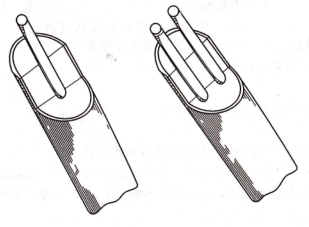

用倒裝的方式替代傳統的用金線去綁定內核的方式,從而縮減電流,讓EMI降到最低。

在RTL輸入和綜合后網表之間進行等效性檢查方面,對FPGASoC的驗證要求可能比ASIC更高。與傳統的ASIC邏輯綜合流程相比,FPGA的精細化、綜合和優化階段通常需要對設計進行更多的修改。

智能電網,ADI同樣擁有完整的解決方案。ADI有帶MPPT的專門器件,可實現在同樣光照情況下獲得最大太陽能能量。

從一個電路來講,有兩個方面的損耗是必須面對的。一個是MOS管開關損耗,另一個是電感作為儲能器件的損耗。

這兩部分的損耗讓你無法克服傳統電源的弊端,效率很難達到93%、94%以上。

如果你把所有運算都放在SoC中運行,那就太慢了。每次模擬可能需要五到七個小時,如果你把多個模擬合并起來,就可以節省時間。

復雜ASIC中使用的同類方法現在正用于復雜的FPGA。隨著這些器件被用于功能安全類型的應用,這變得越來越重要。

這就是形式分析的用武之地,通過形式分析,可以得出錯誤的傳播路徑,然后驗證這些路徑,這些東西非常適合進行形式分析。傳統的FPGA驗證方法幾乎不可能進行這些類型的驗證。

FPGA的大小和復雜性要求其驗證過程類似于ASIC。先進的基于UVM的測試平臺支持模擬,通常也支持仿真。

從自動設計檢查到基于斷言的驗證,以及一系列強大的求解器,形式工具在這里起著關鍵的作用。盡管FPGA確實可以比ASIC更快更便宜地修改,但在大型SoC中檢測和診斷bug的難度意味著必須在進入bring-up階段之前進行徹底的驗證。

用倒裝的方式替代傳統的用金線去綁定內核的方式,從而縮減電流,讓EMI降到最低。

在RTL輸入和綜合后網表之間進行等效性檢查方面,對FPGASoC的驗證要求可能比ASIC更高。與傳統的ASIC邏輯綜合流程相比,FPGA的精細化、綜合和優化階段通常需要對設計進行更多的修改。

智能電網,ADI同樣擁有完整的解決方案。ADI有帶MPPT的專門器件,可實現在同樣光照情況下獲得最大太陽能能量。

從一個電路來講,有兩個方面的損耗是必須面對的。一個是MOS管開關損耗,另一個是電感作為儲能器件的損耗。

這兩部分的損耗讓你無法克服傳統電源的弊端,效率很難達到93%、94%以上。

公網安備44030402000607

公網安備44030402000607