ModeISim仿真軟件設計流程

發布時間:2011/10/9 10:43:12 訪問次數:2385

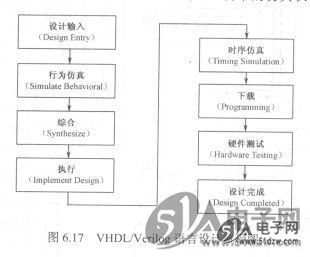

在使用ModeISim仿真軟件之前,首先簡單地介紹一下FPGA設計過程的基本流程,如圖6.17所示。一個大型的項目,這些步驟是不能省略的。這其中行為仿真、時序仿真都需要用到ModelSim。對于一些簡單的項目,也可以用ISE自帶的仿真軟件。 AT24C04

(1)設計輸入(Design Entry)

設計輸入是設計的第一步,其方式有許多種,如VHDLNerilog語言編程,原理圖繪制(Schematic),狀態機或真值表(Truthtable)及波形(Waveform)的輸入等。將設計要求達到的目標采用上述的方式之一進行描述,是設計的第一步。

(2)行為仿真(Simulate Behavioral)

設計輸入利用VHDLNerilog語言完成后,接下來要做的是行為仿真,也有文獻將其稱做功能仿真( Function Simulation)。行為所要達到的目標是功能上的驗證。在做行為仿真時軟件系統會自動對VHDLNerilog程序進衍語法上的檢查、編譯,以及將VHDL/Verilog行級的描述轉化為結構化的門級電路,即綜合( Synthesis)。通過了以上的綜合之后便進入行為仿真步驟。行為仿真也可以在綜合之前進行,但是不少設計者習慣先做綜合之后再進行行為仿真,因為在綜合中附帶了語法上的檢查、編譯等功能,而且修改VHDLNerilog程序語法上的錯誤也比較方便。

進行行為仿真時使用的方法大多是將特定信號輸入設計,然后觀察設計輸出的信號是否符合要求。做行為仿真時可能需要多次反復,對VHDL/Verilog源代碼進行修改,等到所有的功能都正確后,才能進行下一個步驟。

(3)執行(Implement Design)

行為仿真之后就是執行,完成目標系統在器件上的布局與布線(Place&Route)。開發工具可產生含有時序延遲( Timing Delay)的VHDLNerilog網絡表(Netlist)文件,這是最準確的時序延遲文件。

(4)時序仿真(Timing Simulation)

執行完成后,建議在硬件測試之前先做時序仿真,將其作為最后一道把關工作。當然,不做時序仿真,直接將執行結果送到電路板上進行測試也可以。因為做仿真需要輸入正確、完整的測試模型( pattern)。如果測試模型不正確或是其代表性不夠,就算做了仿真也不能確保結果正確。但是,在硬件測試之前,通過軟件進行檢查,確保無誤后再做硬件效率更高一些。

(5)下載

程序將被轉換成位流文件寫入芯片中以實現芯片功能,軟件部分由器件廠商提供的專用軟件完成,硬件則需要使用專用的下載線,通過微機的通信接口與系統板連接。

(6)硬件測試

對實物(芯片及其外圍電路構成的系統)進行實際測試,完成設計。

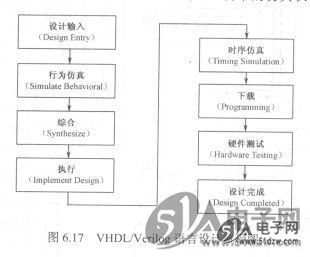

在使用ModeISim仿真軟件之前,首先簡單地介紹一下FPGA設計過程的基本流程,如圖6.17所示。一個大型的項目,這些步驟是不能省略的。這其中行為仿真、時序仿真都需要用到ModelSim。對于一些簡單的項目,也可以用ISE自帶的仿真軟件。 AT24C04

(1)設計輸入(Design Entry)

設計輸入是設計的第一步,其方式有許多種,如VHDLNerilog語言編程,原理圖繪制(Schematic),狀態機或真值表(Truthtable)及波形(Waveform)的輸入等。將設計要求達到的目標采用上述的方式之一進行描述,是設計的第一步。

(2)行為仿真(Simulate Behavioral)

設計輸入利用VHDLNerilog語言完成后,接下來要做的是行為仿真,也有文獻將其稱做功能仿真( Function Simulation)。行為所要達到的目標是功能上的驗證。在做行為仿真時軟件系統會自動對VHDLNerilog程序進衍語法上的檢查、編譯,以及將VHDL/Verilog行級的描述轉化為結構化的門級電路,即綜合( Synthesis)。通過了以上的綜合之后便進入行為仿真步驟。行為仿真也可以在綜合之前進行,但是不少設計者習慣先做綜合之后再進行行為仿真,因為在綜合中附帶了語法上的檢查、編譯等功能,而且修改VHDLNerilog程序語法上的錯誤也比較方便。

進行行為仿真時使用的方法大多是將特定信號輸入設計,然后觀察設計輸出的信號是否符合要求。做行為仿真時可能需要多次反復,對VHDL/Verilog源代碼進行修改,等到所有的功能都正確后,才能進行下一個步驟。

(3)執行(Implement Design)

行為仿真之后就是執行,完成目標系統在器件上的布局與布線(Place&Route)。開發工具可產生含有時序延遲( Timing Delay)的VHDLNerilog網絡表(Netlist)文件,這是最準確的時序延遲文件。

(4)時序仿真(Timing Simulation)

執行完成后,建議在硬件測試之前先做時序仿真,將其作為最后一道把關工作。當然,不做時序仿真,直接將執行結果送到電路板上進行測試也可以。因為做仿真需要輸入正確、完整的測試模型( pattern)。如果測試模型不正確或是其代表性不夠,就算做了仿真也不能確保結果正確。但是,在硬件測試之前,通過軟件進行檢查,確保無誤后再做硬件效率更高一些。

(5)下載

程序將被轉換成位流文件寫入芯片中以實現芯片功能,軟件部分由器件廠商提供的專用軟件完成,硬件則需要使用專用的下載線,通過微機的通信接口與系統板連接。

(6)硬件測試

對實物(芯片及其外圍電路構成的系統)進行實際測試,完成設計。

熱門點擊

熱門點擊

- 三極管結構及工作原理

- 判斷耳機好壞的方法與判斷喇叭好壞的方法基本相

- 貼片元件手工焊接工藝

- 聲控開關電路

- 電燈多地控制線路

- 可變電阻器結構和工作原理

- 電容器的電容誤差

- 音頻功率放大電路

- 印制電路板設計的一般步驟

- 絕緣柵場效應管

推薦技術資料

推薦技術資料

- 自制經典的1875功放

- 平時我也經常逛一些音響DIY論壇,發現有很多人喜歡LM... [詳細]

公網安備44030402000607

公網安備44030402000607