高輸入阻抗低噪聲放大電路

發布時間:2012/8/16 20:38:16 訪問次數:3375

但是,IC化的OP放大器內部的JFET與分立器件的JFET相比,噪聲將性較差。因此,使用FET輸入型OP放大器放大電路難以獲得良好的噪聲特性。

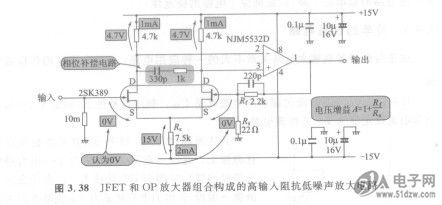

圖3.38是由JFET與具有良好噪聲特性的晶體管輸入型OP放大器組合構成的高輸入阻抗低噪聲放大電路。

初級采用N溝雙JFET 2SK389(東芝)差動放大電路(設定漏極電流比IDSS的最小值小,所以IDSS取哪一檔都可以)。之所以使用雙JFET,是為了減小兩個器件的VG。之差引起的輸出偏移電壓。OP放大器使用雙極晶體管低噪聲輸入OP放大器NJM5532(JRC),從輸出端向初級的差動放大電路的反相輸入端施加負反饋。

由于電源電壓比FET的VG。大很多,所以差動放大電路部分的設計中按照VG=0來計算各部分的電流。由于希望設定各FET的源極電流為ImA(低于所使用的JFET的ID。。的適當值),所以確定在源極電阻R。的值時應使流過R。的電流為2mA(=l mA×2)。如果認為VG=0,那么R。上的電壓降為15V,所以Rs一15V/2mV=7.5kC1。

設定漏極電阻的值時,大約使漏極電流產生的電壓降為幾伏就可以(如果這個電壓降過大,將會使大信號受到限制;反之如果過小,將會超過次級的OP放大器的輸入電壓范圍)。圖3.38的電路中,設定漏極電阻值為4.7k0,,所以漏極電阻上的電壓降為4.7V,

如果將具有電壓增益的電路追加到OP放大器上,全部施加負反饋,電路的穩定性將變壞,有時甚至會產生振蕩。OP放大器內部設計的相位補償電路——為了防止產生振蕩、調整電路內部信號的電路是為了在單獨使用OP放大器的情況下維持電路工作穩定的,所以如果再從外部追加提高電壓增益的電路將會導致電路的工作不穩定。

因此,由于追加了電壓放大電路,就必須追加相位補償電路,以確保電路的穩定性。

但是,IC化的OP放大器內部的JFET與分立器件的JFET相比,噪聲將性較差。因此,使用FET輸入型OP放大器放大電路難以獲得良好的噪聲特性。

圖3.38是由JFET與具有良好噪聲特性的晶體管輸入型OP放大器組合構成的高輸入阻抗低噪聲放大電路。

初級采用N溝雙JFET 2SK389(東芝)差動放大電路(設定漏極電流比IDSS的最小值小,所以IDSS取哪一檔都可以)。之所以使用雙JFET,是為了減小兩個器件的VG。之差引起的輸出偏移電壓。OP放大器使用雙極晶體管低噪聲輸入OP放大器NJM5532(JRC),從輸出端向初級的差動放大電路的反相輸入端施加負反饋。

由于電源電壓比FET的VG。大很多,所以差動放大電路部分的設計中按照VG=0來計算各部分的電流。由于希望設定各FET的源極電流為ImA(低于所使用的JFET的ID。。的適當值),所以確定在源極電阻R。的值時應使流過R。的電流為2mA(=l mA×2)。如果認為VG=0,那么R。上的電壓降為15V,所以Rs一15V/2mV=7.5kC1。

設定漏極電阻的值時,大約使漏極電流產生的電壓降為幾伏就可以(如果這個電壓降過大,將會使大信號受到限制;反之如果過小,將會超過次級的OP放大器的輸入電壓范圍)。圖3.38的電路中,設定漏極電阻值為4.7k0,,所以漏極電阻上的電壓降為4.7V,

如果將具有電壓增益的電路追加到OP放大器上,全部施加負反饋,電路的穩定性將變壞,有時甚至會產生振蕩。OP放大器內部設計的相位補償電路——為了防止產生振蕩、調整電路內部信號的電路是為了在單獨使用OP放大器的情況下維持電路工作穩定的,所以如果再從外部追加提高電壓增益的電路將會導致電路的工作不穩定。

因此,由于追加了電壓放大電路,就必須追加相位補償電路,以確保電路的穩定性。

上一篇:高增益、高輸入阻抗放大電路

上一篇:簡單的恒流電路

公網安備44030402000607

公網安備44030402000607