лК„иЧl

∞l≤ЉХrйg:2013/7/29 19:54:43 ‘LЖЦіќФµ:1831

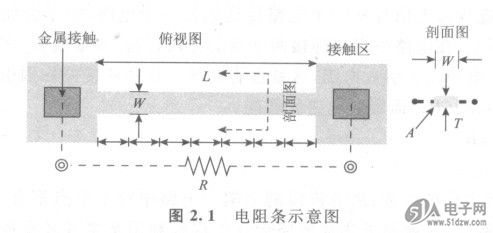

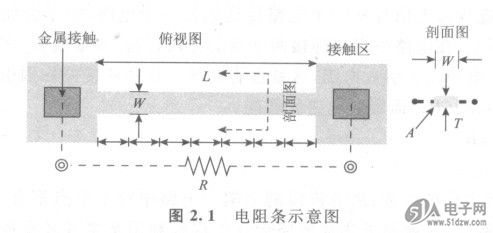

”…”Џ”√Бн÷∆‘млК„иµƒ≤ƒЅѕґЉљЫя^ЊЂ–ƒ‘O”Л£®»зќіљрМўїѓµƒґаЊІєи°ҐЁpУљлsєиµ»£©£ђЋьВГ≈c”√„ч∆чЉю÷Ѓйgї•яBЊАµƒлК„и£®»зљрМўїѓµƒґаЊІєи°ҐљрМўдXµ»£©Ќк»Ђ≤їЌђ£ђP82B715TDґш«“лК„иЧlµƒґЋо^∞ьЇђµЌ„иљ””|Е^”т£®ИD2.1£©°£іЋХr£ђѕаМ¶”Џ‘O”ЛµƒлК„иЧlіу–°£ђ‘цЉ””––ІМТґ»£ђЬp–°”––ІйLґ»£ђПƒґшЬp–°ЅЋя@ВАЕ^”тµƒ’ыуwлК„и£ђ≤Ґ«“яА∞ьЇђЅЋљрМўљ””|£ђњ…“‘µ√µљВчљyµƒ°∞єЈє«о^°±љYШЛµƒлК„иИD–ќ°£є§ЋЗє§≥ћОЯМҐЌ®я^ГЮїѓЅч≥ћБнґ®Ѕx≤ƒЅѕµƒЇсґ»£ђ»з’{’ыґаЊІєиµƒ≥ЅЈeЋў¬ їт’яФU…Ґлsў|‘≠„”µƒЌЋїрХrйg£ђґшЉѓ≥…лК¬Ј‘O”Лє§≥ћОЯґЉ≤їƒ№њЎ÷∆я@–©є§ЋЗЧlЉю°£“тіЋЉѓ≥…лК¬Ј‘O”Лє§≥ћОЯЌ®≥£÷ї–и“™ґ®ЅxнФМ”лК„иµƒйL(L)ЇЌМТ(W)£ђґш≤ї»•ґ®ЅxлК„иµƒЇсґ»(T)£ђя@ЊЌ «Љѓ≥…лК¬Ј‘O”Лє§≥ћОЯГHГH–и“™÷™µј±°М”лК„иRsґш≤ї–и“™ЅЋљв≤ƒЅѕлК„и¬ £Ѓ0µƒ‘≠“т°£±°М”лК„и≈c≤ƒЅѕµƒ±Њ’члК„и¬ йgµƒкPѕµ.

”…”Џ±°М”лК„иіъ±н“їВАЈљЙK£®W°ҐLѕаµ»£©≤ƒЅѕµƒлК„и÷µ£ђґш≤їє№∆д√жЈeћЂ–°£ђ“тіЋ є”√Ј«≥£Јљ±г£ђ±°М”лК„иµƒЈыћЦ±н ЊЮйR°££®sheet resistance£ђ“≤ЈQЮйЈљЙKлК„и£©°£јэ»з£ђЄщУюИD2.1£ђЃФЇц¬‘љ””|Е^µƒлК„и£ђ’ыуwлК„и÷µљьЋ∆Юй7ВАЈљЙKƒ£ЙKіЃ¬У£ђЉі7Rs°£

”…”Џ”√Бн÷∆‘млК„иµƒ≤ƒЅѕґЉљЫя^ЊЂ–ƒ‘O”Л£®»зќіљрМўїѓµƒґаЊІєи°ҐЁpУљлsєиµ»£©£ђЋьВГ≈c”√„ч∆чЉю÷Ѓйgї•яBЊАµƒлК„и£®»зљрМўїѓµƒґаЊІєи°ҐљрМўдXµ»£©Ќк»Ђ≤їЌђ£ђP82B715TDґш«“лК„иЧlµƒґЋо^∞ьЇђµЌ„иљ””|Е^”т£®ИD2.1£©°£іЋХr£ђѕаМ¶”Џ‘O”ЛµƒлК„иЧlіу–°£ђ‘цЉ””––ІМТґ»£ђЬp–°”––ІйLґ»£ђПƒґшЬp–°ЅЋя@ВАЕ^”тµƒ’ыуwлК„и£ђ≤Ґ«“яА∞ьЇђЅЋљрМўљ””|£ђњ…“‘µ√µљВчљyµƒ°∞єЈє«о^°±љYШЛµƒлК„иИD–ќ°£є§ЋЗє§≥ћОЯМҐЌ®я^ГЮїѓЅч≥ћБнґ®Ѕx≤ƒЅѕµƒЇсґ»£ђ»з’{’ыґаЊІєиµƒ≥ЅЈeЋў¬ їт’яФU…Ґлsў|‘≠„”µƒЌЋїрХrйg£ђґшЉѓ≥…лК¬Ј‘O”Лє§≥ћОЯґЉ≤їƒ№њЎ÷∆я@–©є§ЋЗЧlЉю°£“тіЋЉѓ≥…лК¬Ј‘O”Лє§≥ћОЯЌ®≥£÷ї–и“™ґ®ЅxнФМ”лК„иµƒйL(L)ЇЌМТ(W)£ђґш≤ї»•ґ®ЅxлК„иµƒЇсґ»(T)£ђя@ЊЌ «Љѓ≥…лК¬Ј‘O”Лє§≥ћОЯГHГH–и“™÷™µј±°М”лК„иRsґш≤ї–и“™ЅЋљв≤ƒЅѕлК„и¬ £Ѓ0µƒ‘≠“т°£±°М”лК„и≈c≤ƒЅѕµƒ±Њ’члК„и¬ йgµƒкPѕµ.

”…”Џ±°М”лК„иіъ±н“їВАЈљЙK£®W°ҐLѕаµ»£©≤ƒЅѕµƒлК„и÷µ£ђґш≤їє№∆д√жЈeћЂ–°£ђ“тіЋ є”√Ј«≥£Јљ±г£ђ±°М”лК„иµƒЈыћЦ±н ЊЮйR°££®sheet resistance£ђ“≤ЈQЮйЈљЙKлК„и£©°£јэ»з£ђЄщУюИD2.1£ђЃФЇц¬‘љ””|Е^µƒлК„и£ђ’ыуwлК„и÷µљьЋ∆Юй7ВАЈљЙKƒ£ЙKіЃ¬У£ђЉі7Rs°£

…ѕ“ї∆™£ЇќҐлК„”∆чЉю

…ѕ“ї∆™£ЇлК »Ё

ЯбйTьcУф

ЯбйTьcУф

- LC≤Ґ¬У÷C’слК¬ЈµƒћЎьc

- ±°ƒ§лК„иµƒлКЙЇо~ґ®÷µ™ЪЅҐ”Џє¶¬ о~ґ®÷µ

- лК»Ёµƒо~ґ®лКЙЇ

- лКЅч–ЌЯфљz(лК„”є№PL508)≈cлКЙЇ–ЌЯфљz£®

- лК„иЧl

- ѓBЉ”∆ч

- Њя”–ЈАЙЇє¶ƒ№µƒґюШOє№

- лК„”є№ФµУюўYЅѕ

- Ј÷ЎР

- ѕыЪв—b÷√

Ќ∆Ћ]ЉЉ–gўYЅѕ

Ќ∆Ћ]ЉЉ–gўYЅѕ

- ”≤±P љMP3≤•Ј≈∆чљKЉЙЄƒ

- “їіќ≈Љ»їµƒЩCХюќ“љY„RЅЋNE0 2511,ƒ« «“їВАяhЈљµƒ... [‘ФЉЪ]

- 12ќїƒ£ФµёDУQ∆ч (ADC)ЕҐ

- »эљ«ЇѓФµЉ”Ћў∆ч (TMU)ѕµЅ–

- Жќ–Њ∆ђ°∞≈У––≤і°±“їуwїѓЈљ∞ЄћљЊњ

- CoolSiC–§ћЎїщґюШOє№ЉЉ–g

- Љ{ќҐGaN SafeѕµЅ–NV6515£®650

- ≈RљзМІЌ®ƒ£ љ£®CrM£©‘Ф«й

- ґа√љуwЕfћОјн∆чSM501‘Џ«ґ»л љѕµљy÷–µƒС™”√

- їщ”ЏIEEE802.11bµƒEPAЬЎґ»„ГЋЌ∆ч

- QUICCEngine–¬“э«жЌ∆Д”IPЊWљjЄп–¬

- SoC√ж ј∞ЋƒкЇуµƒЃaШIЩC”ц

- MPC8xxѕµЅ–ћОјн∆чµƒ«ґ»л љѕµљyлК‘і‘O”Л

- dsPICЉ∞∆д‘ЏљїЅч„Гоl’{Ћў÷–µƒС™”√—–Њњ

єЂЊW∞≤Вд44030402000607

єЂЊW∞≤Вд44030402000607