基本的多層PCB結構

發布時間:2014/4/24 20:49:36 訪問次數:1275

正如本章所述的幾個例子所證實的,PCB設計者會多次面臨是把關鍵信號層埋在平面之間(目標4)以屏蔽它們,還是把關鍵信號布設在與同一平面相鄰(目標6)的兩層上的選擇。

盡管與流行的習慣相反,我認T356E106K025AT為有重要證據表明:對于高頻電路,良好的EMC性能和信號完整性,將關鍵信號布設在與同一平面相鄰的層上應優于把關鍵信號層埋在平面之間來屏蔽它們。用這種方法可以改進高速PCBs的EMC性能和信號完整性(Archambeault,2002,第191頁)。將信號布設在與同一平面相鄰的層上會顯著減小返回電流路徑的電感,因為大部分PCB設計者不能或者不想在信號跡線的導通孔附近提供平面到平面的導通孔,見16.3.3節的討論。

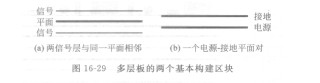

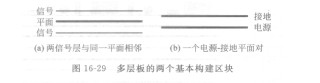

因此這就提出為高層數、高速數字邏輯電路板確定最佳疊層的一般步驟。基本的疊層應該包括兩種基本結構的多重組合:兩個信號層與同一平面相鄰(信號一平面一信號),如圖16-29(a) 所示,以及相鄰的電源和接地平面對,如圖16-29 (b)所示。這兩種結構可以以多種方式組合形成6層或更多層的PCB。

(a)兩信號層與同一平面相鄰 (b) -個電源·接地平面對

圖16 -29多層板的兩個基本構建區塊

例如,圖16-18所示的6層疊層包含兩組圖16-29 (a)所示的基本構建區塊,而圖16-21所示的8層PCB疊層使用了兩組圖16-29(a)所示的基本構建區塊與一組圖16-29 (b)所示的構建區塊組合。

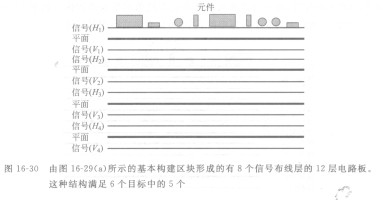

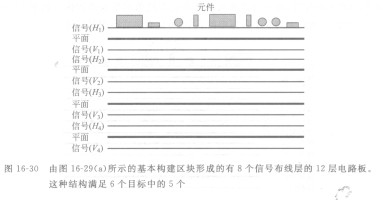

圖16-30表示一個用了四組圖16-29(a)所示的基本構建區塊,有8個布線層的12層電路板。這種疊層沒有相鄰的電源平面和接地平面,所以它只滿足原來6個目標中的5個。

把圖16-29(b)所示的基本構建區塊加到圖16-30歷示的板中心就形成了滿足所有設計目標的14層板。

正如本章所述的幾個例子所證實的,PCB設計者會多次面臨是把關鍵信號層埋在平面之間(目標4)以屏蔽它們,還是把關鍵信號布設在與同一平面相鄰(目標6)的兩層上的選擇。

盡管與流行的習慣相反,我認T356E106K025AT為有重要證據表明:對于高頻電路,良好的EMC性能和信號完整性,將關鍵信號布設在與同一平面相鄰的層上應優于把關鍵信號層埋在平面之間來屏蔽它們。用這種方法可以改進高速PCBs的EMC性能和信號完整性(Archambeault,2002,第191頁)。將信號布設在與同一平面相鄰的層上會顯著減小返回電流路徑的電感,因為大部分PCB設計者不能或者不想在信號跡線的導通孔附近提供平面到平面的導通孔,見16.3.3節的討論。

因此這就提出為高層數、高速數字邏輯電路板確定最佳疊層的一般步驟。基本的疊層應該包括兩種基本結構的多重組合:兩個信號層與同一平面相鄰(信號一平面一信號),如圖16-29(a) 所示,以及相鄰的電源和接地平面對,如圖16-29 (b)所示。這兩種結構可以以多種方式組合形成6層或更多層的PCB。

(a)兩信號層與同一平面相鄰 (b) -個電源·接地平面對

圖16 -29多層板的兩個基本構建區塊

例如,圖16-18所示的6層疊層包含兩組圖16-29 (a)所示的基本構建區塊,而圖16-21所示的8層PCB疊層使用了兩組圖16-29(a)所示的基本構建區塊與一組圖16-29 (b)所示的構建區塊組合。

圖16-30表示一個用了四組圖16-29(a)所示的基本構建區塊,有8個布線層的12層電路板。這種疊層沒有相鄰的電源平面和接地平面,所以它只滿足原來6個目標中的5個。

把圖16-29(b)所示的基本構建區塊加到圖16-30歷示的板中心就形成了滿足所有設計目標的14層板。

上一篇:層以及更多層板

上一篇:一般PCB的設計步驟

熱門點擊

熱門點擊

公網安備44030402000607

公網安備44030402000607