BTABERT的仿真過程及原理

發布時間:2016/7/2 18:16:11 訪問次數:736

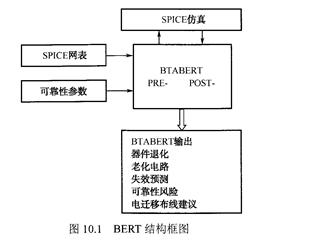

BTABERT(簡稱BERT)是電路可靠性仿真器,由前后兩個處理器ⅡuBERT和POSTBERT組成, AD8018AR通過SPICE仿真器鏈接起來。BERT的輸入文件是sPICE網表文件,其中包括SPICE網表、BERT可靠性參數模型和BERT命令。SPICE仿真器用來產生可靠性計算中所需的電壓與電流,如圖10.1所示。BERT包含4個模擬單元:MOS熱載流子、雙極熱載流子、電遷移和氧化層模擬單元,如圖10.2所示。

這種方法以集成電路的物理失效機理為基礎,包括了IC主要的退化模型(EM、HCI、NBTI和TDDB)。仿真的主要步驟:首先,確定電路中每一種失效機理的可靠性參數(主要通過對單一失效機理的可靠性加速壽命試驗得到),之后利用SPICE等電路仿真器計算器件初始化電參數及器件退化后的電參數,并以此預測器件的退化和失效情況,從而評價電路的可靠性。

通過集成電路的可靠性仿真,發現電路設計中的可靠性薄弱環節,并在電路性能和可靠性之間進行合理的折中,均衡各失效機理的可靠性水平,從而保證整個電路產品的可靠性。

BTABERT(簡稱BERT)是電路可靠性仿真器,由前后兩個處理器ⅡuBERT和POSTBERT組成, AD8018AR通過SPICE仿真器鏈接起來。BERT的輸入文件是sPICE網表文件,其中包括SPICE網表、BERT可靠性參數模型和BERT命令。SPICE仿真器用來產生可靠性計算中所需的電壓與電流,如圖10.1所示。BERT包含4個模擬單元:MOS熱載流子、雙極熱載流子、電遷移和氧化層模擬單元,如圖10.2所示。

這種方法以集成電路的物理失效機理為基礎,包括了IC主要的退化模型(EM、HCI、NBTI和TDDB)。仿真的主要步驟:首先,確定電路中每一種失效機理的可靠性參數(主要通過對單一失效機理的可靠性加速壽命試驗得到),之后利用SPICE等電路仿真器計算器件初始化電參數及器件退化后的電參數,并以此預測器件的退化和失效情況,從而評價電路的可靠性。

通過集成電路的可靠性仿真,發現電路設計中的可靠性薄弱環節,并在電路性能和可靠性之間進行合理的折中,均衡各失效機理的可靠性水平,從而保證整個電路產品的可靠性。

上一篇:集成電路可靠性仿真技術發展多年

上一篇:HCI效應的模擬

公網安備44030402000607

公網安備44030402000607