應力記憶技術的刻蝕

發布時間:2017/11/5 17:01:14 訪問次數:1093

應力記憶技術(sMT)L2Γ已經成為應變硅技術的一種,從65nm△藝節點開始用于增強NMOs的性能。 PCI2050BIZHK通常將具有拉伸應力的SiN層覆蓋在NMC)S上,在尖峰退火后便產生了SMT效應。由于多晶硅和⒏N層導熱系數的差異,在尖峰退火中產生了一個面內拉伸應力和一個縱向壓縮應力,并將其直接傳遞到溝道中。NMOS的性能將受益于這種組合的應變形式,應力的強度與應力薄膜的密度(楊氏模量)直接相關。通常,低密度/孑L隙率意味著有較大的應力被引人到了多晶硅柵中。然而,在sMT應用的早期階段,NMOs性能的提升是以PMOS性能下降為代價的。由于有⒏N層覆蓋,氧化物下面的氫無法在尖峰退火時釋放掉,最終造成PMOS源區和漏區的硼失去活性和外擴。這種PMOS性能的退化與SiN應力層的孔隙率密切相關,并會隨著siN薄膜孔隙率的增加完全消除。然而,這不是NMOS特性所需要的。NM()s特性需要siN薄膜具有更小的孔隙率,以此來引人高應力。

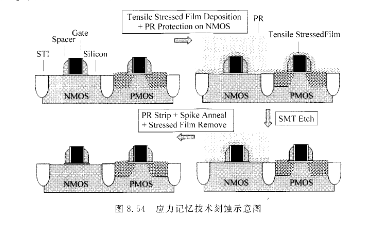

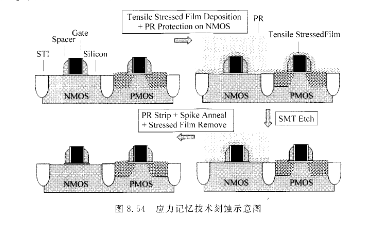

圖8,54顯示的是避免PMOS退化的解決方案之一.即在尖峰退火前,通過干法刻蝕(SMT刻蝕),局部除去應力薄膜。通常的做法是在SiN應力薄膜下面,先生長一層薄氧化層作為停止層。SMT刻蝕主要包含兩個步驟:①采用低壓((20mTorr)和CF!的短時間主刻蝕;②采用CHF3和CH2F2的高選擇比過刻蝕。SMT刻蝕可以在導體刻蝕機中進行,剩下的SiN覆蓋層最后用濕法除去。SMT刻蝕屮的一個問題是SiN層厚在圖形稠密和疏松區域之間的變化。隨著CMOS的等比例縮小,這個問題變得尤為糟糕。因為在小問距的情況下,更薄的siN薄膜常常與穿通的風險以及sGe損失所造成的PM()s退化有關。sN應力層與其停止層之間的高刻蝕選擇比是至關重要的,其引發了對不同薄停止層的評

估。除了11面的SMT刻蝕以外,由于存在于SMT相關的窄寬度效應,所以可能對NMOs上的⒏N層需要-種新的SMT刻蝕。也就是說,在NMC)s屮,可以基于AA(activc area)的寬度調節引入的應力。

應力記憶技術(sMT)L2Γ已經成為應變硅技術的一種,從65nm△藝節點開始用于增強NMOs的性能。 PCI2050BIZHK通常將具有拉伸應力的SiN層覆蓋在NMC)S上,在尖峰退火后便產生了SMT效應。由于多晶硅和⒏N層導熱系數的差異,在尖峰退火中產生了一個面內拉伸應力和一個縱向壓縮應力,并將其直接傳遞到溝道中。NMOS的性能將受益于這種組合的應變形式,應力的強度與應力薄膜的密度(楊氏模量)直接相關。通常,低密度/孑L隙率意味著有較大的應力被引人到了多晶硅柵中。然而,在sMT應用的早期階段,NMOs性能的提升是以PMOS性能下降為代價的。由于有⒏N層覆蓋,氧化物下面的氫無法在尖峰退火時釋放掉,最終造成PMOS源區和漏區的硼失去活性和外擴。這種PMOS性能的退化與SiN應力層的孔隙率密切相關,并會隨著siN薄膜孔隙率的增加完全消除。然而,這不是NMOS特性所需要的。NM()s特性需要siN薄膜具有更小的孔隙率,以此來引人高應力。

圖8,54顯示的是避免PMOS退化的解決方案之一.即在尖峰退火前,通過干法刻蝕(SMT刻蝕),局部除去應力薄膜。通常的做法是在SiN應力薄膜下面,先生長一層薄氧化層作為停止層。SMT刻蝕主要包含兩個步驟:①采用低壓((20mTorr)和CF!的短時間主刻蝕;②采用CHF3和CH2F2的高選擇比過刻蝕。SMT刻蝕可以在導體刻蝕機中進行,剩下的SiN覆蓋層最后用濕法除去。SMT刻蝕屮的一個問題是SiN層厚在圖形稠密和疏松區域之間的變化。隨著CMOS的等比例縮小,這個問題變得尤為糟糕。因為在小問距的情況下,更薄的siN薄膜常常與穿通的風險以及sGe損失所造成的PM()s退化有關。sN應力層與其停止層之間的高刻蝕選擇比是至關重要的,其引發了對不同薄停止層的評

估。除了11面的SMT刻蝕以外,由于存在于SMT相關的窄寬度效應,所以可能對NMOs上的⒏N層需要-種新的SMT刻蝕。也就是說,在NMC)s屮,可以基于AA(activc area)的寬度調節引入的應力。

公網安備44030402000607

公網安備44030402000607