先進工藝對Cu cMP的挑戰

發布時間:2017/11/11 17:48:47 訪問次數:1572

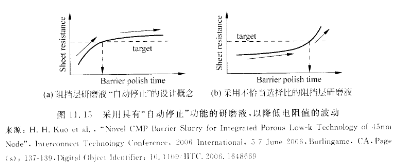

在先進I藝中,隨著金屬連線的尺寸越來越小,微小的銅線高度的變化,就會造Q62702A950成很大的電阻值和電容值的變化。在銅拋光中銅去除量的波動是電阻值波動的主要來源之一。所以先進工藝對銅拋光的第」大挑戰是如何降低電阻值R、的波動。銅拋光中銅去除量的波動是其WIW/WID/WTW非均勻性,以及其凹陷(dishing)與侵蝕(crosion)所形成的綜合效果。當WIW/WID/WTW非均勻性得到改進,銅的去除量則可降低;另外當主要由凹陷與侵蝕引起的上一層的非平整度降低,下一層銅拋光中的銅去除量也可大大降低。銅拋光中WIW/WID/WTW非均勻性以及凹陷與侵蝕的改善依賴于很多囚素,它是研磨液、拋光墊和拋光墊修整過程在各種拋光條件下相互作用的綜合效果。第=步阻擋層的研磨對R、波動的影響尤為明顯。所以通過終點檢測和APC)提高其控制能力,通過拋光墊和拋光墊修整條件的改善減少新舊拋光墊間的差異以及阻擋層研磨拋光選擇性的優化、表面形貌修正能力的改善,對降低R、波動至關重要。另外,在先進工藝中,介質層會由帽封層(如TE(B)和低乃材料所組成。為了提高拋光的控制能力,降低WTW的R、波動,低慮材料的拋光速率應該低于帽封層的拋光速率。采用這種具有自動停止(self stop)功能的研磨液,也成為近年來的發展趨勢之一,以降低電阻值的波動,見圖11.15。

在先進I藝中,隨著金屬連線的尺寸越來越小,微小的銅線高度的變化,就會造Q62702A950成很大的電阻值和電容值的變化。在銅拋光中銅去除量的波動是電阻值波動的主要來源之一。所以先進工藝對銅拋光的第」大挑戰是如何降低電阻值R、的波動。銅拋光中銅去除量的波動是其WIW/WID/WTW非均勻性,以及其凹陷(dishing)與侵蝕(crosion)所形成的綜合效果。當WIW/WID/WTW非均勻性得到改進,銅的去除量則可降低;另外當主要由凹陷與侵蝕引起的上一層的非平整度降低,下一層銅拋光中的銅去除量也可大大降低。銅拋光中WIW/WID/WTW非均勻性以及凹陷與侵蝕的改善依賴于很多囚素,它是研磨液、拋光墊和拋光墊修整過程在各種拋光條件下相互作用的綜合效果。第=步阻擋層的研磨對R、波動的影響尤為明顯。所以通過終點檢測和APC)提高其控制能力,通過拋光墊和拋光墊修整條件的改善減少新舊拋光墊間的差異以及阻擋層研磨拋光選擇性的優化、表面形貌修正能力的改善,對降低R、波動至關重要。另外,在先進工藝中,介質層會由帽封層(如TE(B)和低乃材料所組成。為了提高拋光的控制能力,降低WTW的R、波動,低慮材料的拋光速率應該低于帽封層的拋光速率。采用這種具有自動停止(self stop)功能的研磨液,也成為近年來的發展趨勢之一,以降低電阻值的波動,見圖11.15。

上一篇:主流阻擋層研磨液的主要成分及作用

上一篇:采用低霪材料做介質成為發展的方向

熱門點擊

熱門點擊

- 互連層RC延遲的降低

- Cu CMP產生的缺陷

- 俄歇電子

- 熱點檢測失效定位

- 先進工藝對Cu cMP的挑戰

- 相位襯度

- 應力記憶技術的刻蝕

- 具有高MEEF的圖形會減少全芯片的工藝窗口

- 與常規CMOS工藝兼容的鎳的全硅化工藝是自對

- 水罩相對硅片禁止時的接觸角

推薦技術資料

推薦技術資料

- 自制經典的1875功放

- 平時我也經常逛一些音響DIY論壇,發現有很多人喜歡LM... [詳細]

公網安備44030402000607

公網安備44030402000607