VI-22B-EV輸出端L的波形

發布時間:2019/10/26 12:05:11 訪問次數:807

VI-22B-EV計結果生成器件的下載文件 ,并為模擬和編程產生輸出文件。

編譯過程說明

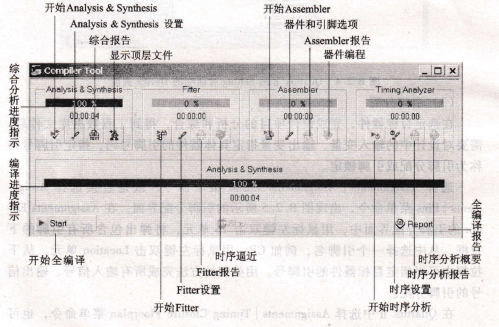

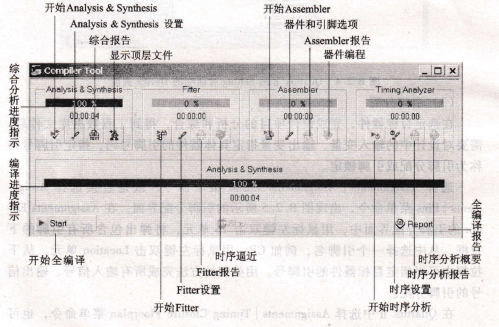

使用tools compiler tool 菜單命令,出現quartus 2的編譯器窗口,如圖B.2.3所示.該窗口包含了對設計文件處理的全過程."analysis & synthesis"(分析和綜合)模塊創建工程項目數據庫,對設計文件進行邏輯綜合,完成設計邏輯到器件到資源的技術映射.計邏輯到器件資源的技sembler”模塊產生多種Ⅱ的“Analysis&輯的性能分析。“EDA Netlist Writer”模塊產生用于第三方EDA工具的網表文件及其他輸出文件。

開始Analysis&s”姐esis開始Assembler&synlcsis設置器件和引腳選項顯示頂層文件器件編程序逼近F1tt∝設置時序設置開始Fittcr,始時序分析圖B.2.3.

(2)編譯器選項設置,Quartus Ⅱ的編譯器窗口,對編譯器選項進行設置,可以控制編譯過程。Quartus Ⅱ編譯器設置選項中,可以指定目標器件,對“Analysis&synthesis”選項和“Fitter”選項等進行設置。所有設置選項均可在該對話框中找到,選擇assignments|Setungs。

試用一片74x154譯碼器和必要的與非門,設計一個乘法器電路,實現2位二進制數相乘,并輸出結果。74x154示意圖如圖.

用邏輯門對74HC42的功能做修改,增加低電平使能輸人功能。要求當使能端為高電平時,所有輸出為高電平。

七段顯示譯碼電路如圖題4.4.14(a)所示,對應圖題4.4.14(b)所示輸人波形,

試確定顯示器顯示的字符序列是什么?

數據選擇器如圖題4,4.15所示,并行輸人數據J3J2JI J0=1010,控制端X=0,A1AO的態序分別為00、01、10、11,試畫出輸出端L的波形。

數據選擇器如圖題4.4.16所示,當f=0,f=J1=j2=1時,有z=sI+SI so的關系,證明該邏輯表達式的正確性。

應用圖題4.4.16所示的電路產生邏輯函數F=s1+sO。

設計一4選1數據選擇器。數據輸人是f。、J1、r2、r3,數據輸出是y,4個控

制信號為s。、sl、s2、S3。要求只當sJ=1時,幾與y接通,且由另一控制信號E作為該選擇器的使能信號。

畫出由反相器、兩輸人與門和或門實現的邏輯電路。

選擇一合適的三態門作為輸出級。

試用4選1數據選擇器74HC153產生邏輯函數L(A,B,C)=∑m(1,2,6,7)。

74HC151的連接方式,輸人波形如圖題4.4.20所示,畫出輸出端

應用74HC151實現如下邏輯函數:

(1) I=ABC+ABC+⒕BC

(2)z=(AOB)0C

應用已介紹過的中位通道選擇信號的控制下,能將的一個輸出端,其示意圖如圖題其功能是在4出端中相對應.

VI-22B-EV計結果生成器件的下載文件 ,并為模擬和編程產生輸出文件。

編譯過程說明

使用tools compiler tool 菜單命令,出現quartus 2的編譯器窗口,如圖B.2.3所示.該窗口包含了對設計文件處理的全過程."analysis & synthesis"(分析和綜合)模塊創建工程項目數據庫,對設計文件進行邏輯綜合,完成設計邏輯到器件到資源的技術映射.計邏輯到器件資源的技sembler”模塊產生多種Ⅱ的“Analysis&輯的性能分析。“EDA Netlist Writer”模塊產生用于第三方EDA工具的網表文件及其他輸出文件。

開始Analysis&s”姐esis開始Assembler&synlcsis設置器件和引腳選項顯示頂層文件器件編程序逼近F1tt∝設置時序設置開始Fittcr,始時序分析圖B.2.3.

(2)編譯器選項設置,Quartus Ⅱ的編譯器窗口,對編譯器選項進行設置,可以控制編譯過程。Quartus Ⅱ編譯器設置選項中,可以指定目標器件,對“Analysis&synthesis”選項和“Fitter”選項等進行設置。所有設置選項均可在該對話框中找到,選擇assignments|Setungs。

試用一片74x154譯碼器和必要的與非門,設計一個乘法器電路,實現2位二進制數相乘,并輸出結果。74x154示意圖如圖.

用邏輯門對74HC42的功能做修改,增加低電平使能輸人功能。要求當使能端為高電平時,所有輸出為高電平。

七段顯示譯碼電路如圖題4.4.14(a)所示,對應圖題4.4.14(b)所示輸人波形,

試確定顯示器顯示的字符序列是什么?

數據選擇器如圖題4,4.15所示,并行輸人數據J3J2JI J0=1010,控制端X=0,A1AO的態序分別為00、01、10、11,試畫出輸出端L的波形。

數據選擇器如圖題4.4.16所示,當f=0,f=J1=j2=1時,有z=sI+SI so的關系,證明該邏輯表達式的正確性。

應用圖題4.4.16所示的電路產生邏輯函數F=s1+sO。

設計一4選1數據選擇器。數據輸人是f。、J1、r2、r3,數據輸出是y,4個控

制信號為s。、sl、s2、S3。要求只當sJ=1時,幾與y接通,且由另一控制信號E作為該選擇器的使能信號。

畫出由反相器、兩輸人與門和或門實現的邏輯電路。

選擇一合適的三態門作為輸出級。

試用4選1數據選擇器74HC153產生邏輯函數L(A,B,C)=∑m(1,2,6,7)。

74HC151的連接方式,輸人波形如圖題4.4.20所示,畫出輸出端

應用74HC151實現如下邏輯函數:

(1) I=ABC+ABC+⒕BC

(2)z=(AOB)0C

應用已介紹過的中位通道選擇信號的控制下,能將的一個輸出端,其示意圖如圖題其功能是在4出端中相對應.

上一篇:HDSP-431G設計項目的編譯

上一篇:TLE4271-2引腳分配

公網安備44030402000607

公網安備44030402000607