HDSP-431G設計項目的編譯

發布時間:2019/10/25 22:00:34 訪問次數:618

HDSP-431G上述工作完成后,由軟件自動完成布局與布線工作,它以最優的方式對邏G件布局,并準確地完成元件之間的連線。

時序仿真使用包含延時信息的編譯網表,不僅測試邏輯功能,還測試設計的邏輯在目標器件中最差情況下的時序關系,它和器件的實際工作情況基本一致,因此對整個設計項目進行時序仿真,分析其時序關系,評估設計的性能是非常必要的。

器件的編程與測試,在對設計的文件進行處理時,軟件會自動產生供編程用的數據文件。對CPLD器件,編程文件為熔絲圖文件;而對FPGA器件,編程文件為位流數據文件。對具有在系統編程功能的器件,可以使用相應的編程軟件,通過編程電纜直接將編程數據寫入到器件中。對沒有在系統編程接口的器件,則需要使用專用編程器,才能對器件編程。對器件的編程完成后,需要對器件的功能進行

實際測試。

對于熟悉MAX+PLUS Ⅱ的用戶,在啟動Quartus Ⅱ軟件后,選擇Tods|Customize…菜單命令,在對話框的Genera1頁面選擇MAX+PLUS Ⅱ選項,單擊Apply按鈕后,重新啟動Quartus Ⅱ軟件,則此時主窗口圖形用戶界面與

MAX+PLUS Ⅱ軟件的界面類似。

下面以Ⅴerilog HDL設計十進制計數器為例,從輸入設計文件、設計項目的編譯、設計項目的仿真驗證和器件編程四個方面對Quartus Ⅱ軟件的使用進行簡單介紹。受篇幅所限,原理圖(或稱為方塊圖)輸人方式不作介紹,詳細使用方法可以參考軟件幫助文檔。

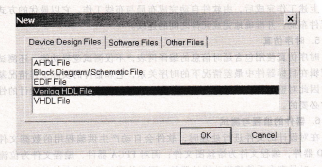

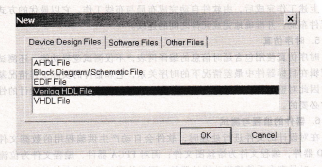

使用向導建立新工程,并輸入設計文件,啟動Quartus Ⅱ軟件后,從Fne菜單下選擇New Project Wizzard,按照提示輸人設計項目的路徑,項目名稱以及頂層模塊的名稱。然后選擇Fne|New...命令,出現圖B.2.1所示界面,選擇設計文件的輸入方式,例如Verilog HDLFile,則會打開輸人編輯窗口,輸入設計文件后,保存文件。

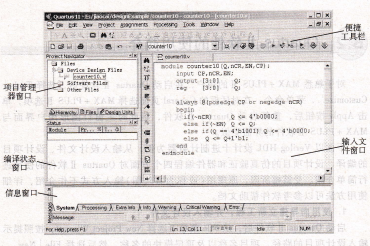

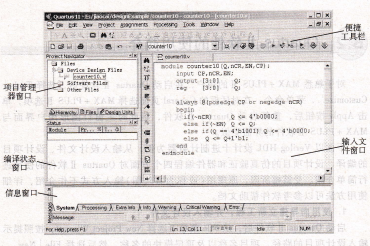

在上述操作完成后,出現圖B.2.2所示的主窗口。窗口結構與一般Win~

dows中應用程序的窗口類似,主要由標題信息欄、主菜單欄、圖標便捷工具欄、窗口主體以及底部的輔助信息提示欄組成。在窗口主體中,左邊的是項目

圖B.2,2 Quartus Ⅱ主窗口受篇幅所限,窗口中的菜單功能和使用方法可以參考軟件幫助文檔,此處不再贅述。

設計項目的編譯,Quartus Ⅱ編譯器主要完成設計項目的檢查和邏輯綜合,將項目的最終設成.

HDSP-431G上述工作完成后,由軟件自動完成布局與布線工作,它以最優的方式對邏G件布局,并準確地完成元件之間的連線。

時序仿真使用包含延時信息的編譯網表,不僅測試邏輯功能,還測試設計的邏輯在目標器件中最差情況下的時序關系,它和器件的實際工作情況基本一致,因此對整個設計項目進行時序仿真,分析其時序關系,評估設計的性能是非常必要的。

器件的編程與測試,在對設計的文件進行處理時,軟件會自動產生供編程用的數據文件。對CPLD器件,編程文件為熔絲圖文件;而對FPGA器件,編程文件為位流數據文件。對具有在系統編程功能的器件,可以使用相應的編程軟件,通過編程電纜直接將編程數據寫入到器件中。對沒有在系統編程接口的器件,則需要使用專用編程器,才能對器件編程。對器件的編程完成后,需要對器件的功能進行

實際測試。

對于熟悉MAX+PLUS Ⅱ的用戶,在啟動Quartus Ⅱ軟件后,選擇Tods|Customize…菜單命令,在對話框的Genera1頁面選擇MAX+PLUS Ⅱ選項,單擊Apply按鈕后,重新啟動Quartus Ⅱ軟件,則此時主窗口圖形用戶界面與

MAX+PLUS Ⅱ軟件的界面類似。

下面以Ⅴerilog HDL設計十進制計數器為例,從輸入設計文件、設計項目的編譯、設計項目的仿真驗證和器件編程四個方面對Quartus Ⅱ軟件的使用進行簡單介紹。受篇幅所限,原理圖(或稱為方塊圖)輸人方式不作介紹,詳細使用方法可以參考軟件幫助文檔。

使用向導建立新工程,并輸入設計文件,啟動Quartus Ⅱ軟件后,從Fne菜單下選擇New Project Wizzard,按照提示輸人設計項目的路徑,項目名稱以及頂層模塊的名稱。然后選擇Fne|New...命令,出現圖B.2.1所示界面,選擇設計文件的輸入方式,例如Verilog HDLFile,則會打開輸人編輯窗口,輸入設計文件后,保存文件。

在上述操作完成后,出現圖B.2.2所示的主窗口。窗口結構與一般Win~

dows中應用程序的窗口類似,主要由標題信息欄、主菜單欄、圖標便捷工具欄、窗口主體以及底部的輔助信息提示欄組成。在窗口主體中,左邊的是項目

圖B.2,2 Quartus Ⅱ主窗口受篇幅所限,窗口中的菜單功能和使用方法可以參考軟件幫助文檔,此處不再贅述。

設計項目的編譯,Quartus Ⅱ編譯器主要完成設計項目的檢查和邏輯綜合,將項目的最終設成.

公網安備44030402000607

公網安備44030402000607